# **Deeds:**

# A Tool for Digital Design and Embedded System Training

Giuliano Donzellini & Domenico Ponta

donzie@unige.it, ponta@unige.it

DIBE – Department of Biophysical and Electronic Engineering

University of Genoa, Italy

http://www.esng.dibe.unige.it/deeds/

Symposium on Embedded Systems and Applications

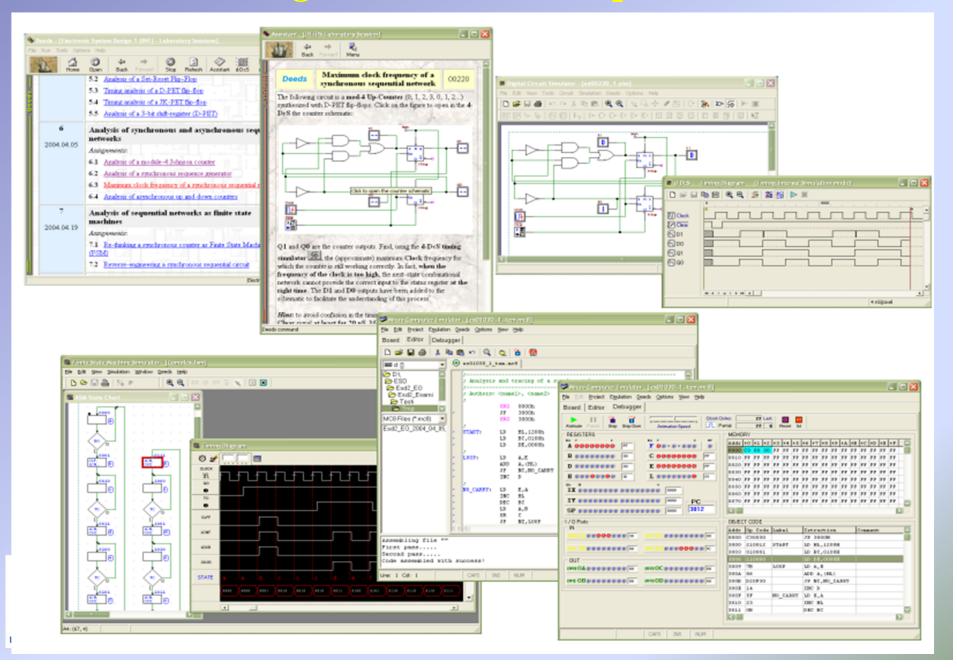

### **Deeds learning environment:** a panoramic view

## Learning digital design today

- The enormous and growing complexity of today's digital systems is putting new demands on education.

- EDA techniques are the core of a digital system development process, while traditional design and prototyping have lost their roles.

- EDA techniques are finding their way in engineering education.

- Professional EDA tools are available at very favourable conditions for educational institutions, and successfully used in engineering courses.

electronic systems and networking group

## Starting from zero: how?

- A growing number of teachers introduce Hardware Description Languages and EDA tools in basic, introductory courses.

- Beginner students do not possess the skills and the frame of mind of the professional designers, whom the EDA tools are made for.

- We suspect that the use of professional tools and Hardware Description Languages in introductory courses may hide from learners important basic issues.

- Nevertheless, to achieve some familiarity with EDA techniques is a necessary target of a digital design course, even an introductory one.

Symposium on Embedded Systems and Applications

### Learning the basics: "from zero to one"

- The design and simulation suite that we developed, *Deeds*, represents our answer to the question: how?

- *Deeds* embodies our pedagogical approach to teaching and learning digital design *"from zero to one"*

- Our target is to prepare students to the use of current and future EDA tools by building a solid understanding of the principle of digital design.

- This means to guide a learner, with no previous knowledge, typically in a one year long course, to achieve the foundation for designing embedded systems.

electronic systems and networking group

## **Deeds:** Digital Electronics Education and Design Suite

- *Deeds* is developed at DIBE, University of Genoa

- The suite is composed by three simulators and a wide collection of associated *learning material* to learn-by-doing and practice with:

- Combinational and sequential logic networks

- Finite state machine design

- Embedded microcomputer interfacing and programming

# **Deeds:** the simulation tools

- d-DcS

- d-FsM

- d-McE

- Digital Circuit Simulator Finite State Machine Simulator

- Microcomputer Board Emulator

Symposium on Embedded Systems and Applications

- The three simulators are *fully integrated*

- It is possible to design and simulate *digital systems* composed by *standard logic*, *finite state machines* and *microcomputers*

- It is therefore possible to understand the interaction among the hardware and software components of *embedded systems*

University of Genoa

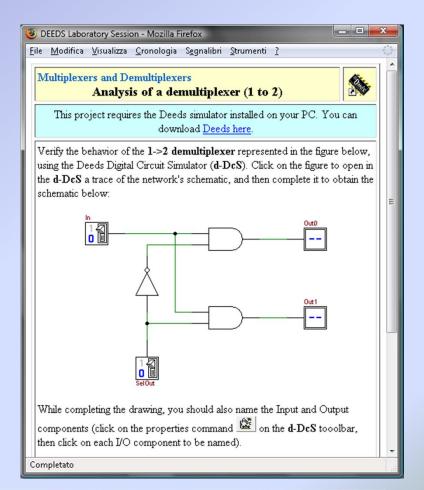

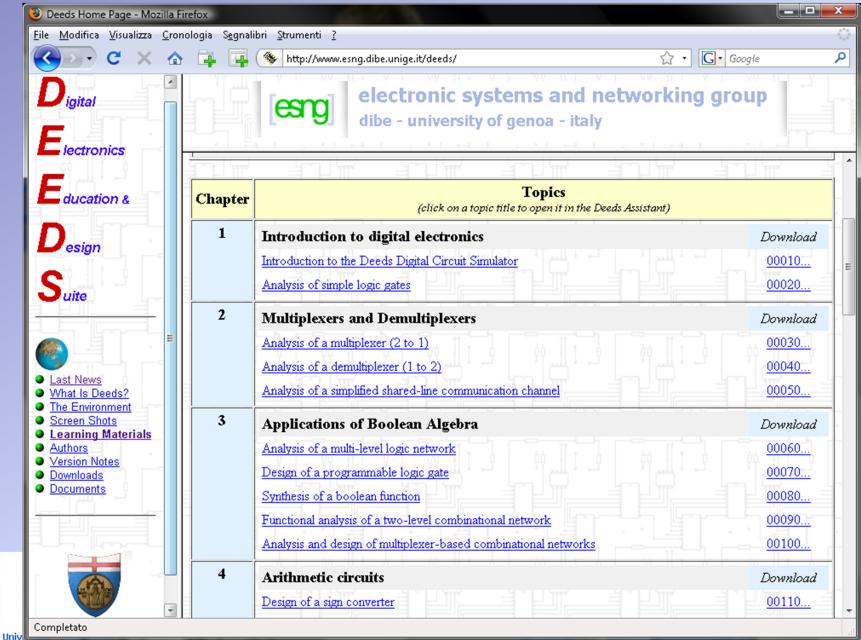

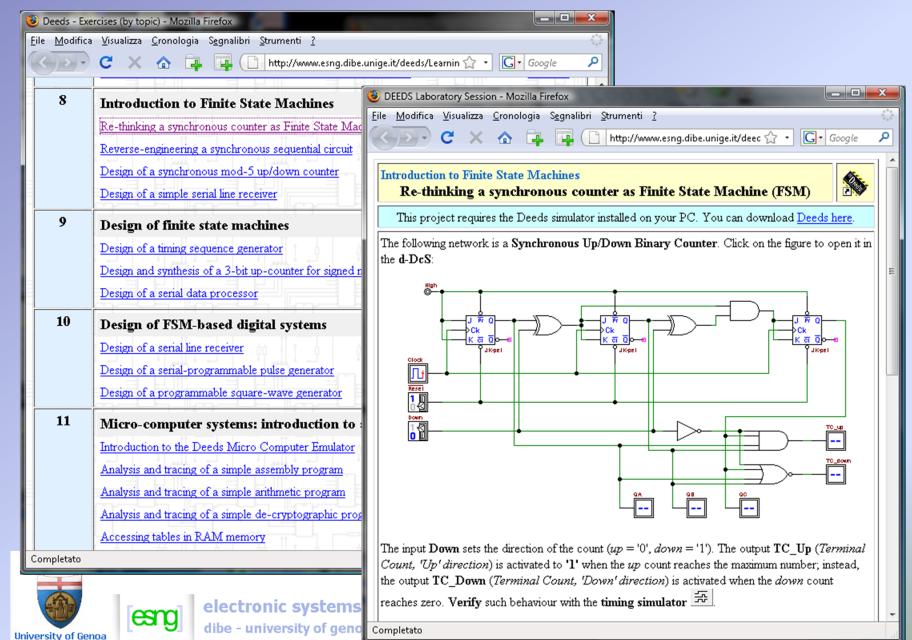

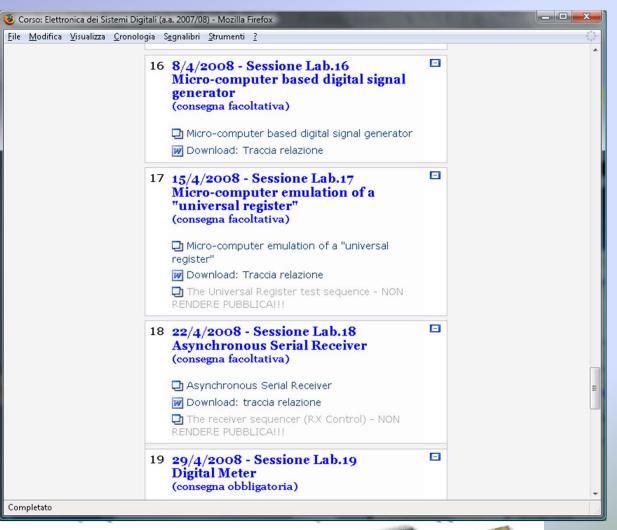

# **Deeds:** the learning materials

- A *laboratory session* based on *Deeds* appears as web pages with text and figures

- Many of the schematics and visual objects are connected to the editing and simulation tools of *Deeds*

- The web pages guide the learner in executing the assignment

Symposium on Embedded Systems and Applications

### **Deeds:** projects' list by topic

### **Deeds:** project assignment

10

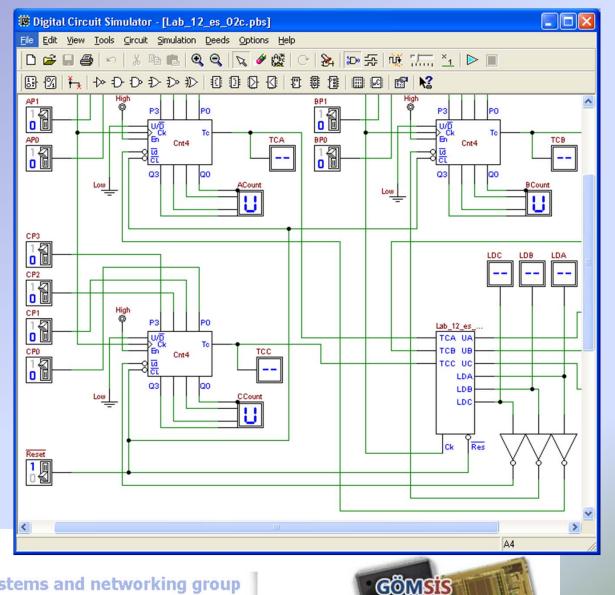

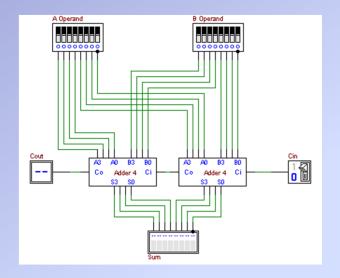

## **Deeds:** the d-DcS Digital Circuit Simulator

- The d-DcS is a digital circuit simulator specifically developed with educational needs in mind

- The d-DcS has been designed to be easy to use, while maintaining quasiprofessional features

- The user interface is intuitive

- The choice of digital components is based on their logical function, not on commercial lines

- Two simulation mode are available:

a) Interactive Animationb) Timing diagram

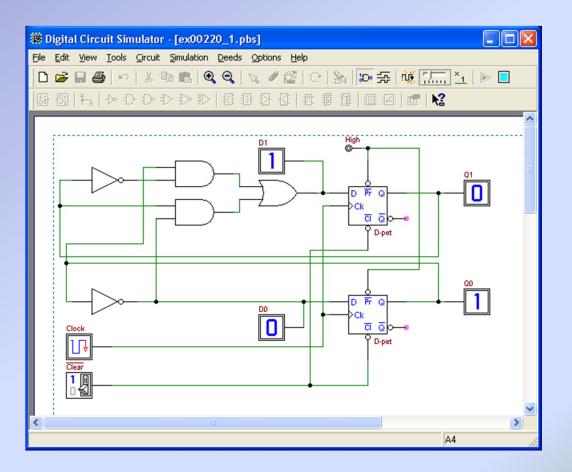

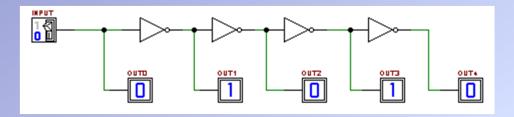

### **Deeds:** the d-DcS Interactive Animation

- In the interactive animation mode the simulator processes input commands and displays output values

- The input components, on the left of the figure, are a clock and a logical level generator

- The level generator is represented as a switch, toggled by a mouse click

- The clock can be activated edge by edge or continously

- Output components display the values of the selected nodes (four in the figure)

#### Symposium on Embedded Systems and Applications

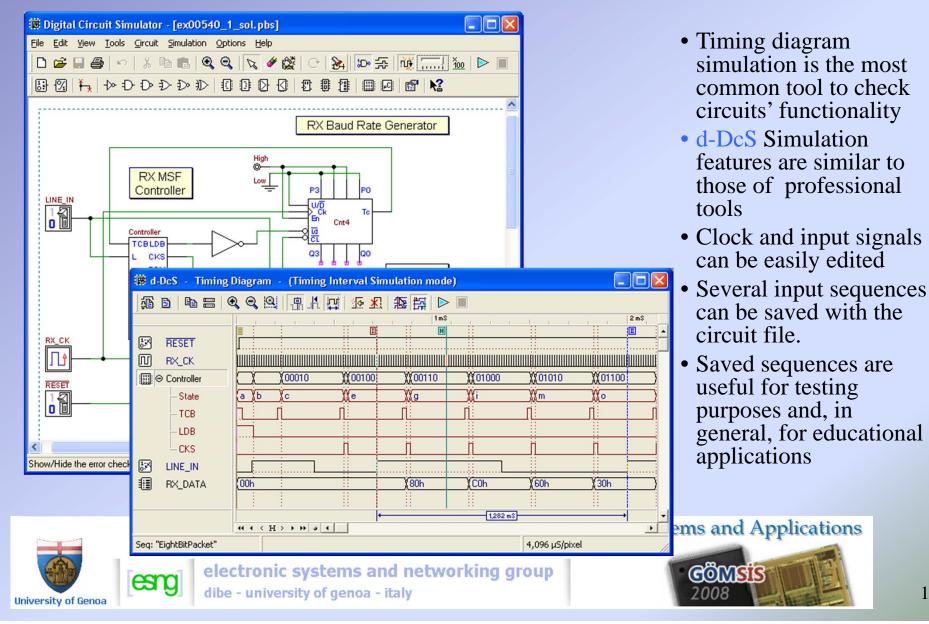

# **Deeds:** the d-DcS Timing Diagram

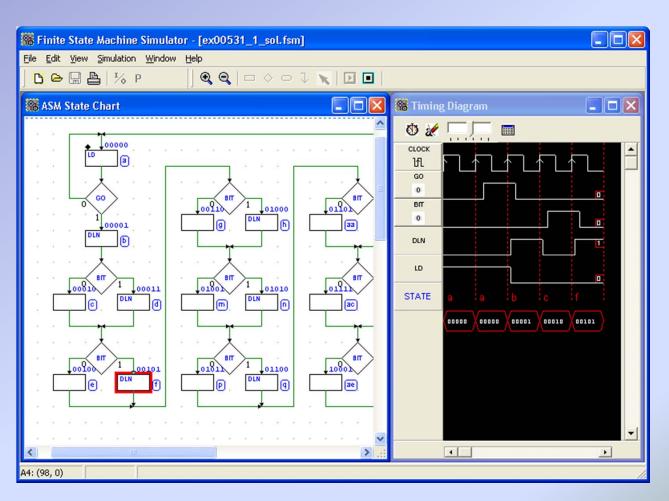

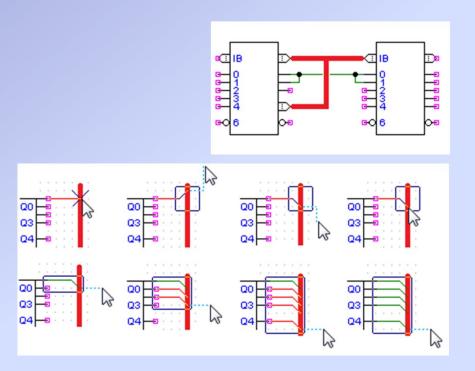

# **Deeds:** the d-FsM Simulator

- Finite state machines (FSM) are designed with ASM charts

- Algorithms can be functionally tested (with a timing diagram), without circuit syntesis

- A FSM produced with the d-FsM tool can be used as a component by the d-DcS

- A FSM can also be exported in VHDL language, to allow reusing it in professional design tools

#### Symposium on Embedded Systems and Applications

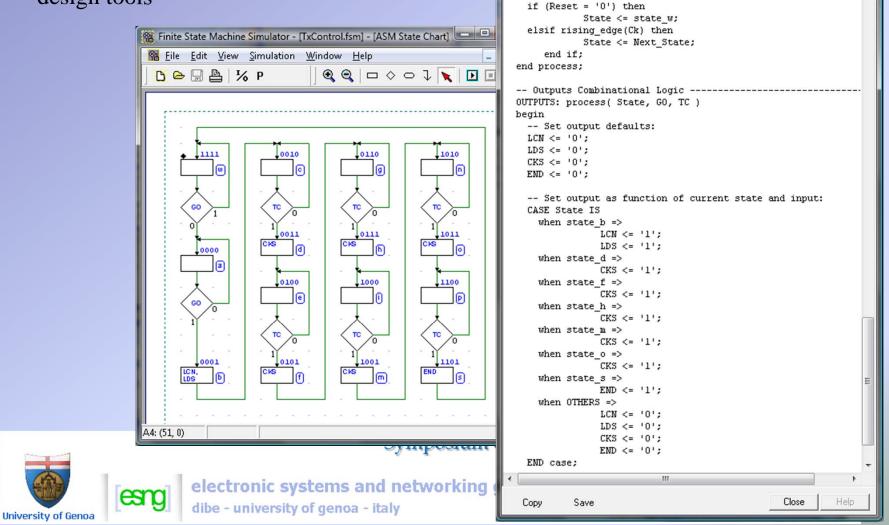

# **Deeds:** the d-FsM to VHDL encoder

M VHDL Code

begin

-- State Register ------REG: process( Ck, Reset )

• A FSM can also be exported in VHDL language, to allow reusing it in professional design tools

15

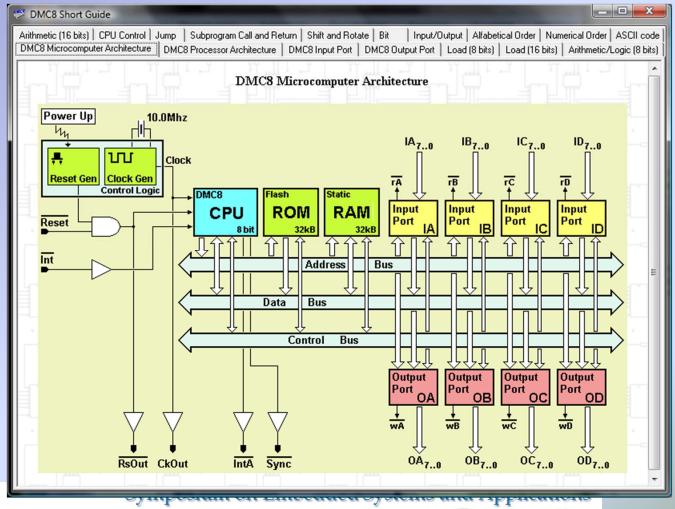

# **Deeds:** the d-McE µC emulator

- The *d-McE* micro-computer emulator is based on an 8bits microprocessor, RAM and ROM and a simple parallel input/output port system

- It interfaces the external world through four input and four output parallel ports

- Address and data busses are not available outside, but port control signals are available to extend the ports

- Clock, Reset and Interrupt signal are available

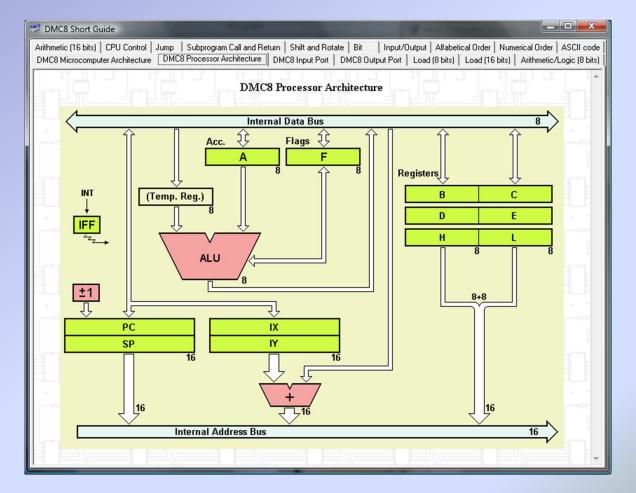

# **Deeds:** the CPU architecture

- The 8-bit micro-processor is the DMC8

- **DMC8** emulates a simplified version of the well-known Z80-CPU

- The use of a "state of the art" CPU is not compatible with our pedagogical targets

#### Symposium on Embedded Systems and Applications

# **Deeds:** the d-McE code editor

- The micro-computer emulator allows to edit assembly code with syntax highlighting

- Assembling, linking and loading operation are transparent to the user

| 🧼 h                                        | Aicro Compu                            | iter Em   | ulator - [Ex0106                 | :8_1_sol.mc8]                                           |    |  |  |  |

|--------------------------------------------|----------------------------------------|-----------|----------------------------------|---------------------------------------------------------|----|--|--|--|

| Eile                                       | Edit Project                           | Emulat    | ion <u>O</u> ptions <u>V</u> iew | Help                                                    |    |  |  |  |

| Board Editor Debugger                      |                                        |           |                                  |                                                         |    |  |  |  |

|                                            |                                        | 1 u       |                                  |                                                         |    |  |  |  |

|                                            |                                        | )<br>予    |                                  | .   👝   🎦   🔞                                           |    |  |  |  |

|                                            | ;                                      |           |                                  |                                                         | ~  |  |  |  |

|                                            | ;===================================== |           | rrupt links                      |                                                         |    |  |  |  |

|                                            | ;========                              |           |                                  |                                                         |    |  |  |  |

|                                            |                                        | ORG       | 0000h                            | ;Reset                                                  |    |  |  |  |

| 1                                          |                                        | JP<br>ORG | START<br>0038h                   | ;Interrupt                                              |    |  |  |  |

|                                            |                                        | JP        | INTERRUPT                        | ;incertupe                                              |    |  |  |  |

|                                            |                                        |           |                                  |                                                         |    |  |  |  |

|                                            | ;                                      |           |                                  |                                                         |    |  |  |  |

|                                            | ; Main Pro                             | -         |                                  |                                                         |    |  |  |  |

|                                            | ( <sup></sup>                          | ORG       | 0100h                            |                                                         |    |  |  |  |

| •                                          | START:                                 | LD        | SP,OFFFFh                        | ;Init. Stack Pointer                                    |    |  |  |  |

|                                            | ;<br>.Tnitieliz                        | ation.    | variables, po                    | rta intervint                                           |    |  |  |  |

|                                            | , 1111 CI GI I Z                       |           | CLRLEDS                          | ics, incertape                                          |    |  |  |  |

| · ·                                        |                                        | LD        | (VALUE),A                        | ; init received value                                   |    |  |  |  |

|                                            |                                        | LD        | (DISABLE),A                      | THE THE AVERAGE AVERAGE                                 |    |  |  |  |

|                                            |                                        | IN<br>EI  | A, (RXDATA)                      | ;reset RX Interrupt Sequencer<br>;enable CPU Interrupts |    |  |  |  |

|                                            | ;                                      |           |                                  | , and a constrained                                     |    |  |  |  |

| •                                          | MAINLOOP:                              | LD        | A, (DISABLE)                     |                                                         |    |  |  |  |

| · ·                                        |                                        | 0R        | A<br>                            |                                                         | ~  |  |  |  |

| < 2                                        | <                                      |           |                                  |                                                         | >  |  |  |  |

|                                            | Assembling file "Ex01068_1_sol.mc8"    |           |                                  |                                                         |    |  |  |  |

|                                            | First pass                             |           |                                  |                                                         |    |  |  |  |

| -> Code assembled and loaded with success! |                                        |           |                                  |                                                         |    |  |  |  |

| Line                                       | 1 Col: 1                               |           | CAPS                             | INS NUM                                                 |    |  |  |  |

| Line:                                      | 1 COL 1                                |           | CMPD                             |                                                         | 11 |  |  |  |

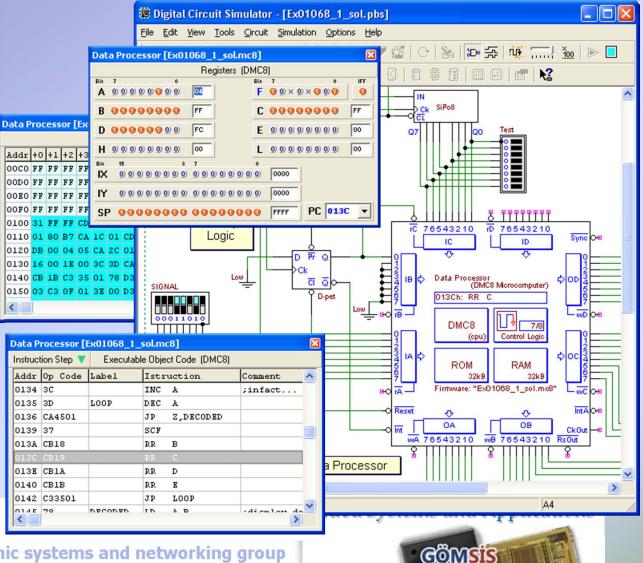

# **Deeds:** the d-McE debugger

- The micro-computer emulator allows to debug the program step-by-step or in animation mode

- The interactive visual debugger shows memory, registers and ports contents

- The tool allows a full control of the microcomputer, including I/O operations

| Alicro Computer Emulator - [Ex01068_1_sol.mc8]                                                                                                                                               |                                                      |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---|

| Eile Edit Project Emulation Options View Help                                                                                                                                                |                                                      |   |

| Board Editor Debugger                                                                                                                                                                        |                                                      |   |

| V         II         II         III         III         Clock Cycle           Step         Animate         Run         Pause         Over         Animation Speed         III         Partia |                                                      |   |

| Registers                                                                                                                                                                                    | Memory                                               |   |

| Bit 7 0 Bit 7 0 IFF<br>A 0 0 0 0 0 0 0 0 14 F 0 0 × 0 × 0 0 0 0 0                                                                                                                            | Addr +0 +1 +2 +3 +4 +5 +6 +7 +8 +9 +A +B +C +D +E +F | ^ |

|                                                                                                                                                                                              | 0000 C3 00 01 FF |   |

| B 0000000 FF C 0000000 FF                                                                                                                                                                    | OOLO FF          |   |

| D 0 0 0 0 0 0 0 12 E 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                     | 0020 FF          |   |

| H 0 0 0 0 0 0 0 11 L 0 0 0 0 0 0 02                                                                                                                                                          | 0030 FF          |   |

| Bit 15 \$ 7 0                                                                                                                                                                                | 0050 FF          |   |

| IX 000000000000000000000000000000000000                                                                                                                                                      | 0060 FF          |   |

| IY 000000000000000000000000000000000000                                                                                                                                                      | 0070 FF          | ~ |

| SP 0000000 0000000 FFFF PC 013R -                                                                                                                                                            |                                                      | Ť |

| I / O Ports                                                                                                                                                                                  | Object Code                                          |   |

| IN Bit 7 0 Bit 7 0                                                                                                                                                                           | Addr Op Code Label Istruction Comment                | ^ |

| [00] IA 0000000 24 [02] IC 00000000 10                                                                                                                                                       | 0132 1E00 LD E,0                                     |   |

|                                                                                                                                                                                              | 0134 3C INC A ;infact                                |   |

|                                                                                                                                                                                              | 0135 3D LOOP DEC A                                   |   |

| OUT Bit 7 0 Bit 7 0                                                                                                                                                                          | 0136 CA4501 JP Z,DECODED                             |   |

| [00] OA 00000000 00 [02] OC 00000000 00                                                                                                                                                      | 0139 37 SCF<br>013A CB18 RR B                        |   |

| [01] OB 00000000 00 [03] OD 00000000 00                                                                                                                                                      | 013C CB19 RR C                                       |   |

|                                                                                                                                                                                              | OI3E CBIA RR D                                       |   |

| Info                                                                                                                                                                                         | 0140 CB1B RR E                                       |   |

| [0149h] User Break-Point encountered                                                                                                                                                         | 0142 C33501 JP LOOP                                  | ~ |

| [013Ah] User Break-Point encountered                                                                                                                                                         |                                                      |   |

| Address = 008Fh CAPS INS NUM                                                                                                                                                                 |                                                      | - |

| Address = 008Fh CAPS INS NUM                                                                                                                                                                 |                                                      |   |

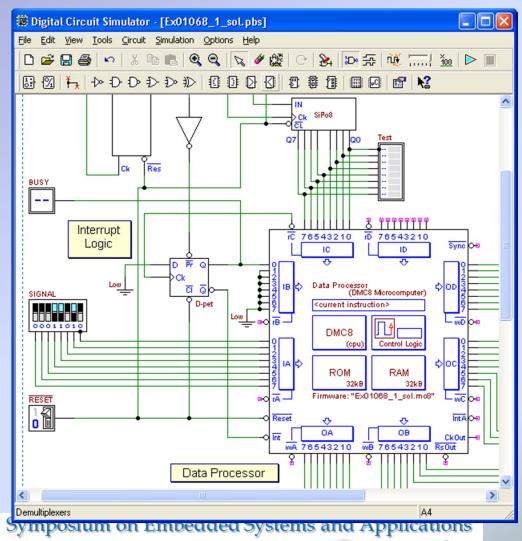

## The micro-computer as d-DcS component

- The micro-computer is a component of the library of the d-DcS

- A digital circuit, embedding one or more micro-computers, can be simulated by the d-DcS

- The embedded micro-computer can be programmed with the d-McE tool.

# The micro-computer in the d-DcS

- The functionality of the d-McE debugger is available in the d-DcS

- Memory, CPU registers, port status can be monitored during simulation of a digital system that embeds one or more micro-computer

- Through the debugger windows we can analyse the program logic while testing the hardware behaviour

2008

## **Deeds in practice at University of Genoa**

- **Deeds**, as support to traditional teaching, has been extensively used in our institution by thousands of students of the first and second year of the *information engineering curricula*. This practice has been very successful, as demonstrated over the years by the evaluation procedures.

- As tool for Project Based Learning only courses, *Deeds* has been used in conjunction with the NetPro (Network Based Project Learning), a European project of the Leonardo DaVinci programme, for both local and international courses.

- Students' and teachers' feedback has been very encouraging. Several colleagues from European universities have adopted Deeds in their teaching.

University of Genoa

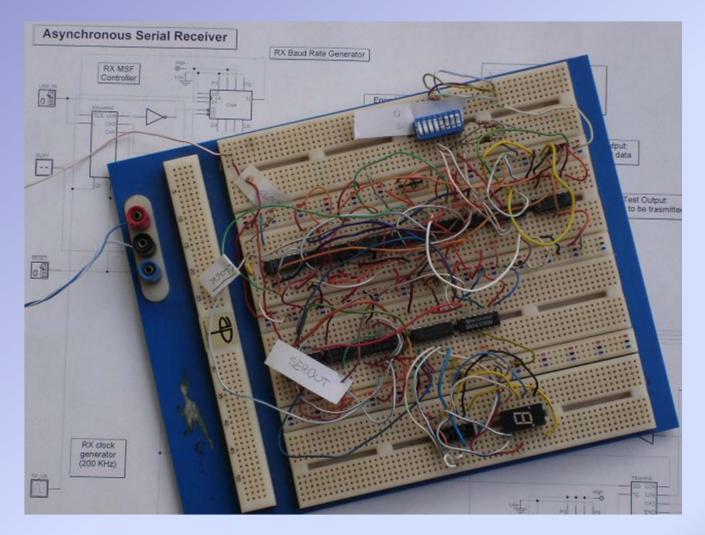

### Not long time ago... a breadboard of a serial transmitter!

Symposium on Embedded Systems and Applications

# **Blended learning with Deeds**

- Our largest experience has taken place using Deeds in a blended learning environment, where traditional lectures coexist with a problem-based laboratory.

- The laboratory is delivered, at the same time, in a PC classroom, with tutorial assistance, or in distant mode, through Internet.

- Students can access the laboratory from home.

- In both cases the delivery is supported by a Learning Management System (NetPro at the beginning, then Moodle)

### Moodle Learning Management System (LMS)

- The integration of *Deeds* material with a *Learning Management System* (LMS) provides added value for teachers and students alike.

- Teachers can keep track of students' activity, provide news and guidance, have access to the project deliverables and, generally, take advantage of the *LMS* features to manage the course.

### Moodle Learning Management System (LMS)

- Decds Learning Material is delivered through the LAND that supports laboratory activity;

- Students get a large amount of flexibility in the execution of the projects, that may be local or remote, exchange information with their peers and get help by the teachers through the discussion forums.

### Students' Project Report

- "Templates" that facilitate the preparation of the laboratory report are provided with each laboratory session

- Students find on the *report template*: truth tables & maps ready to be filled, space to paste circuit schematics, ASM diagrams, timing diagrams, comments and so on

- Reports are uploaded on the *Learning Management System*

| he         | 🔄 lab02_template.doc - Microsoft Word                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Elle Modifica Visualizza Inserisci Formato Strumenti Iabella MathType Finestra ?                                                                                                                                                                                     |

|            | □ 😂 🖬 🕒 🖾 🔍 🖤 🎎   ½ 🗈 🏝 🟈 🔊 • 🔍 •   🧶 😡 ∃= Ⅲ   ¶   🕮 Lettura 👘                                                                                                                                                                                                       |

| h          | $\frac{1}{2} \underbrace{A_1} \text{ Normale + Arial, } 10  \mathbf{G}  \mathbf{C}  \mathbf{S}  \mathbf{X}_1 \equiv \mathbf{\Xi} \equiv \mathbf{\Xi} \mid \mathbf{\Xi} \mid \mathbf{\Xi} \mid \mathbf{\Xi} \cdot \mathbf{X}_2 \cdot \mathbf{A}_2 \cdot \mathbf{X}_2$ |

| h          | ····1····2····13····4····                                                                                                                                                                                                                                            |

|            | Assignment 2.1: Analysis of a multiplexer (2 to 1)                                                                                                                                                                                                                   |

|            | 1) Schematic<br>paste here your schematic                                                                                                                                                                                                                            |

|            | 2) Truth Table                                                                                                                                                                                                                                                       |

|            | <u>fill</u> the truth table                                                                                                                                                                                                                                          |

| 5          | <u>Sel</u> Inl In2 Out                                                                                                                                                                                                                                               |

| ste        |                                                                                                                                                                                                                                                                      |

| 510        |                                                                                                                                                                                                                                                                      |

|            |                                                                                                                                                                                                                                                                      |

|            |                                                                                                                                                                                                                                                                      |

|            | Assignment 2.2: Analysis of a de-multiplexer (1 to 2)                                                                                                                                                                                                                |

|            | 1) Schematic                                                                                                                                                                                                                                                         |

|            | paste here your schematic                                                                                                                                                                                                                                            |

|            | 2) Truth Table                                                                                                                                                                                                                                                       |

|            | fill the truth table In SelOut OutO Out1                                                                                                                                                                                                                             |

| e <b>m</b> |                                                                                                                                                                                                                                                                      |

|            |                                                                                                                                                                                                                                                                      |

|            |                                                                                                                                                                                                                                                                      |

|            | 3) Timing Diagram                                                                                                                                                                                                                                                    |

|            | Ţ<br>■ ☐ ☐ ☐ ☐ Û ♥ ♥                                                                                                                                                                                                                                                 |

| 0          | i Disegno 🔹 🗟   Eorme 🔹 🔪 🔪 🖸 🔿 🔛 📣 🛟 💁 🥥 🛃 🖄 🔹 🚣 🖛 🛱 🚇 🎯 🥊                                                                                                                                                                                                          |

| Symposi    | Pg Sez A Ri Col REG REV EST SSC Inglese (Aus 🔐                                                                                                                                                                                                                       |

|            |                                                                                                                                                                                                                                                                      |

| i network  | king group                                                                                                                                                                                                                                                           |

| aly        | 2008                                                                                                                                                                                                                                                                 |

## **Deeds** is a resource for teachers

- Deeds is not a commercial product, it is free for academic institution

- Extensive learning material available in English

- Teachers can developed new *project assignments* with any web page editor

#### Symposium on Embedded Systems and Applications

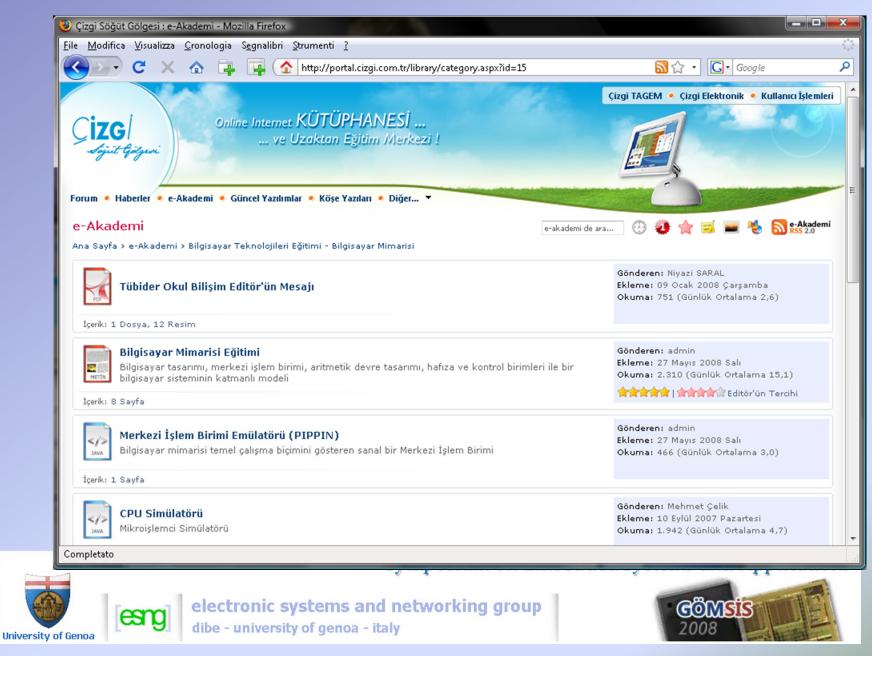

## **Deeds** is a shared resource for teachers

- Deeds *project assignments* have been shared among European schools (within the European Union LeonardoDaVinci NetPro project)

- Sharing projects among teachers is very cost-effective, promotes cooperation and homogeneisation of courses and programs, encourages students exchange (Erasmus)

- *Project assignments* have been translated in other languages, last of which is *Turkish*

University of Genoa

#### Deeds on Turkish web pages...

#### Deeds on Turkish web pages...

| Image: Sogut Gölgesi : e-Akademi - Mozilla Firefox         File       Modifica       Visualizza       Cronologia       Segnalibri       Strumenti       ?                                                                    |                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 🔇 💭 C 🗙 🏠 📮 🐺 🏠 http://portal.cizgi.com.tr/library/category.aspx?id=15                                                                                                                                                       | 📓 🗘 🔹 🖸 🖌 Google                                                                                              |

| MIPS R2000 CPU Simülatörü<br>MIPS R2000 CPU Simülatörü<br>İçerik: 1 Sayfa, 1 Dosya, 5 Resim                                                                                                                                  | Gönderen: Mehmet Çelik<br>Ekleme: 12 Eylül 2007 Çarşamba<br>Okuma: 1.166 (Günlük Ortalama 2,8)                |

| SimHYMN Simülatörü<br>SİmHYMN simülatörü ile CPU'nun bir program parçasını nasıl simüle ettiğini görebilirsiniz.<br>İçerik: 1 Sayfa, 2 Dosya, 6 Resim                                                                        | Gönderen: Mehmet ÇELİK<br>Ekleme: 06 Aralık 2007 Perşembe<br>Okuma: 403 (Günlük Ortalama 1,2)                 |

| Logisim<br>Sayısal Devreler Simülatörü                                                                                                                                                                                       | Gönderen: Mehmet Çelik<br>Ekleme: 14 Eylül 2007 Cuma<br>Okuma: 4.677 (Günlük Ortalama 11,4)                   |

| İçerik: 41 Sayfa, 3 Dosya, 12 Resim           Logisim ile Bilgisayar Mimarisi Dersi           Jean REBIFFE (İngilizce)                                                                                                       | Gönderen: Mehmet ÇELİK<br>Ekleme: 27 Kasım 2007 Salı<br>Okuma: 784 (Günlük Ortalama 2,3)                      |

| İçerik: 12 Dosya, 12 Resim                                                                                                                                                                                                   |                                                                                                               |

| Deeds Simülatörü<br>Deeds, dijital elektronik sistemleri için araç ve öğrenim materyali sunan bir simulatör setidir.                                                                                                         | <b>Gönderen:</b> admin<br><b>Ekleme:</b> 28 Mayıs 2008 Çarşamba<br><b>Okuma:</b> 3.318 (Günlük Ortalama 21,8) |

| İçerik: 52 Sayfa<br>Hades Simülatörü<br>Hades hem temel sayısal sistem tasarımını öğretmek hem de sistem simülasyonu ve donanım/yazılım<br>benzetimi üzerine çalışmalar için bir araç olarak kullanılır.<br>İçerik: 25 Sayfa | Gönderen: admin<br>Ekleme: 29 Mayıs 2008 Perşembe<br>Okuma: 2.082 (Günlük Ortalama 13,8)                      |

| Completato                                                                                                                                                                                                                   |                                                                                                               |

| University of Genoa                                                                                                                                                                                                          | COMSIS<br>2008                                                                                                |

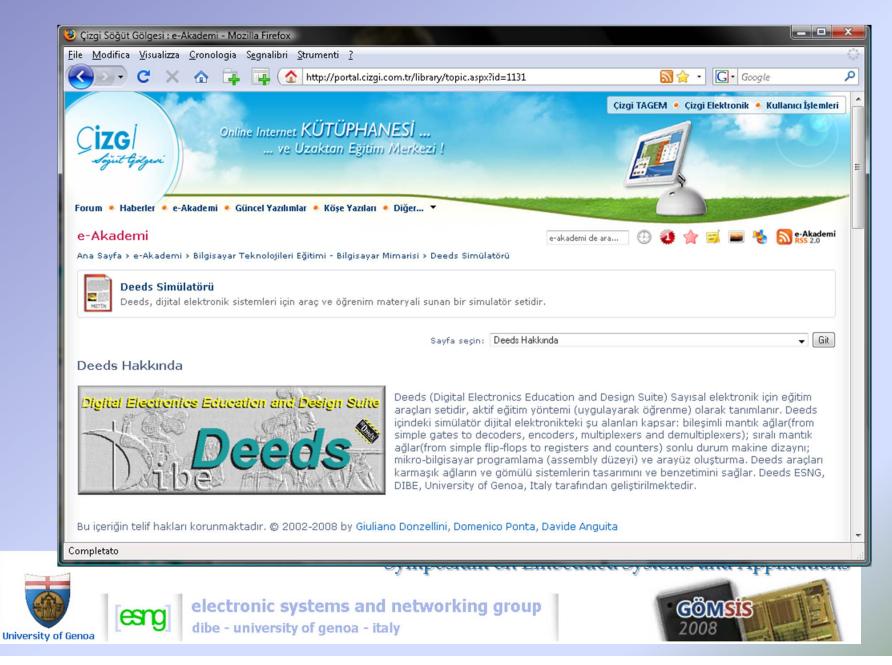

#### Deeds on Turkish web pages...

#### Deeds Learning Material in Turkish: partial view

University of Genoa

33

#### Deeds Learning Material : an example

## **Deeds to introduce Embedded System Design**

- Let's assume that students have familiarised themelves with analysis and design of systems based on *standard logic circuits*, *finite state machines* and a *microcomputer*.

- The knowledge and skills gained in the previous phases are necessary to understand and design embedded systems in a *bottom-up approach*.

- We believe that the task of *introducing* embedded systems can be made easier by starting with the analysis of a pedagogically-oriented implementation.

- On the following slides, we present an exercise where students are facing a mixed work of *analysis* of the hardware structure and *design* of the microcomputer controlling software.

University of Genoa

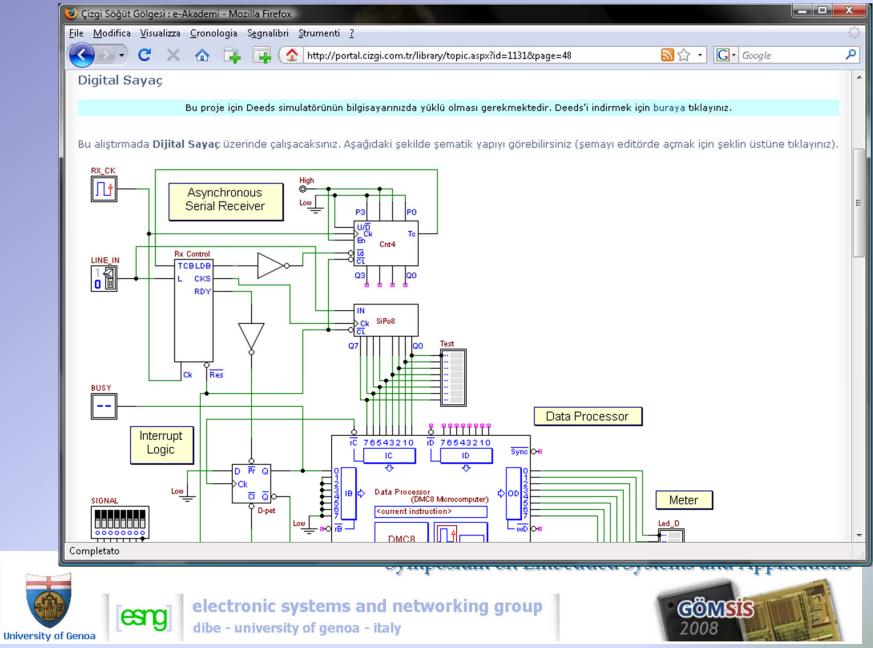

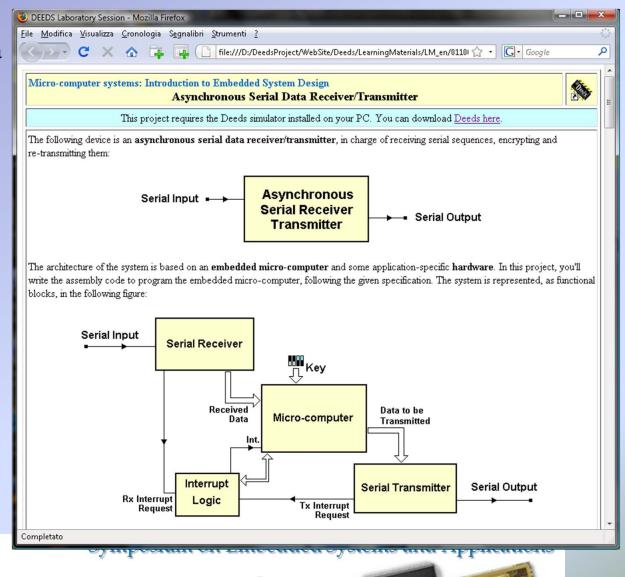

## Embedded System: a project assignment

- The system is a Asynchronous Serial Data Receiver – Transmitter.

- The receiver and the transmitter are implemented by hardware.

- The micro-computer buffers and encrypts data.

- The system hardware is given; the software must be written.

- The target is to understand dynamics and interactions among modules of an *interruptdriven system*.

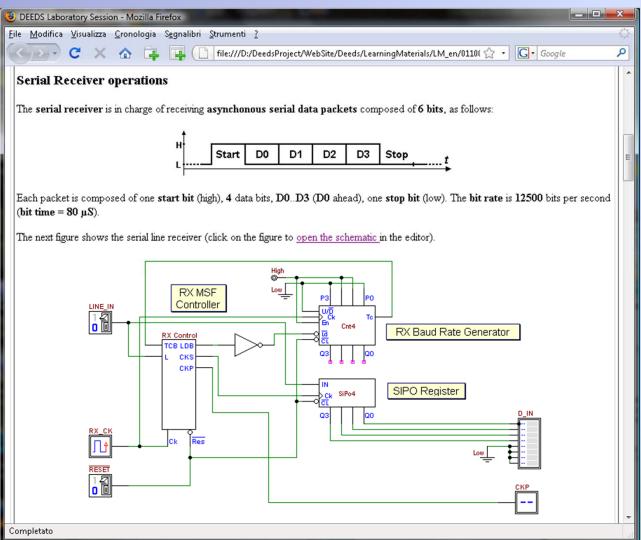

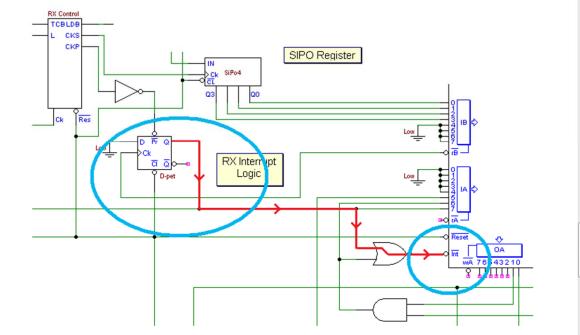

## The asynchronous serial receiver

- The assignment explains the operation of the serial receiver

- The receiver system is built around a sequencer controlling a counter and a shift register

- The schematic must be opened with the *d-DcS simulator*

- Students should understand the behaviour of the system

Symposium on Embedded Systems and Applications

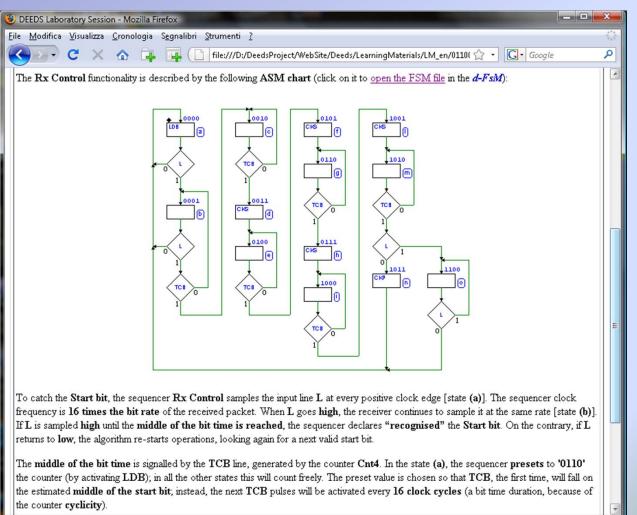

### The serial receiver controller

- The assignment provides the ASM chart of the state machine controlling the receiver

- The algorithm can be opened in the *d*-*F*sM *simulator*

- The analysis of the algorithm is essential to understand the system timing

- The *d-DcS simulator* is used to complete the analysis of the receiver module

Completato

Symposium on Embedded Systems and Applications

dibe - university of genoa - italy

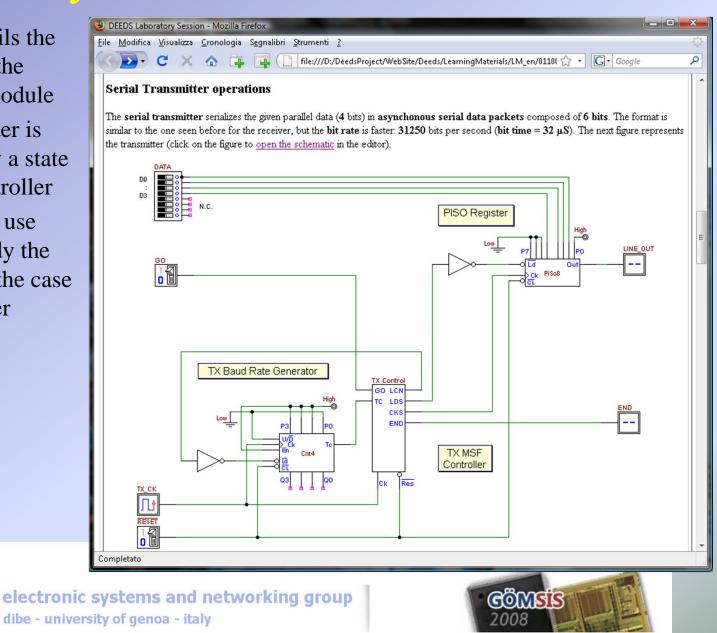

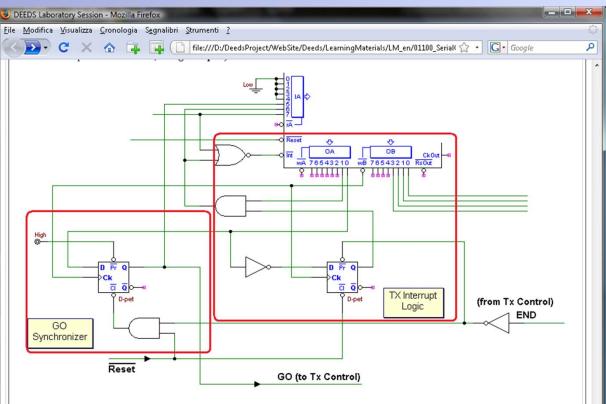

### The asynchronous serial transmitter

- The text details the operation of the transmitter module

- The transmitter is sequenced by a state machine controller

- Students will use **Deeds** to study the system as in the case of the receiver

### The serial transmitter controller

- Also for the transmitter, the text provides the *ASM chart* of the controlling *state machine*

- The analysis of the transmitter module is carried out with the *d*-*F*sM *simulator* and *d*-*D*cS *simulator*

DEEDS Laboratory Session - Mozilla Firefox

Eile Modifica Visualizza Cronologia Segnalibri Strumenti ?

🔊 🗣 🗶 🏠 📮 📮 ( 🗋 file:///D:/DeedsProject/WebSite/Deeds/LearningMaterials/LM\_ 😭 🔹 🗔 🛛 Google

1010

#### Asynchronous Serial Data Transmitter functionality

The transmitter is composed by the Cnt4 counter, the SiPo8 shift register and the Tx Control sequencer.

The binary counter Cnt4 is synchronized by the TX\_CK clock at 500 KHz. The counter is cabled to count down cyclically. Every time the outputs Q3..Q0 reach the number '0000', the output TC (terminal count) is activated, resulting in a pulse on TC every 16 clock cycles. The cyclic activation of TC is used by the TX Control sequencer to synchronize the transmission of data bits at the given bit/rate (31250 b/s = 500 KHz / 16). When the LCN signal is activated by the sequencer, the counter is preset to the value '1110' (from on the inputs P3..P0) to begin the transmission sequence (see the description of the TX Control sequencer).

The **PiSo8** register, when the signal LDS is activated, loads in parallel the four data bits D3..D0, together with a bit set to '1' (P0, the Start bit) and the others to '0' (including the Stop bit, P5). At the same time, the load operation starts the transmission, since it sets LINE\_OUT to '1', as Start bit of the serial sequence. Then, every time the register clock (CKS) is pulsed, the bits are shifted "right", so transmitting the next bit of the data packet on LINE\_OUT.

The TX Control sequencer functionality is described by the ASM chart reported on the side (click on it to open the FSM file in the *d*-*F*sM). The first two states, (w) and (a) are in charge of waiting for the positive edge of the GO command. In state (b), LCN presets the counter Cnt4 and LDS loads the data in the PiSO8 shift register. The couple of states (c) and (d) wait for TC from the counter, i.e. waits 32  $\mu$ S before activating CKS, the clock of the shift register.

State sequence from (e) to (o) repeats four times the same task, and the shift register is progressively emptied (data is transmitted bit after bit, each one every  $32 \ \mu S$ ).

After the transmission of the stop bit, the output END is generated (s) to signal the end of transmission.

dibe - university of gen

40

Q

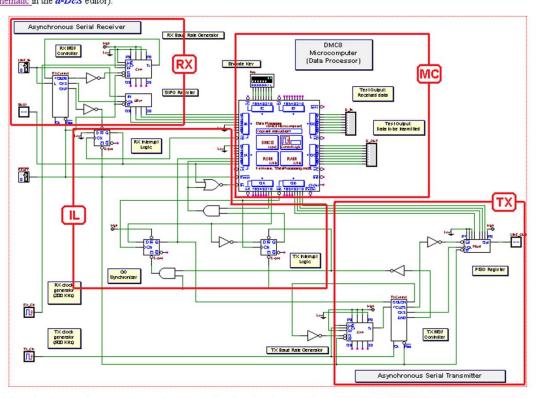

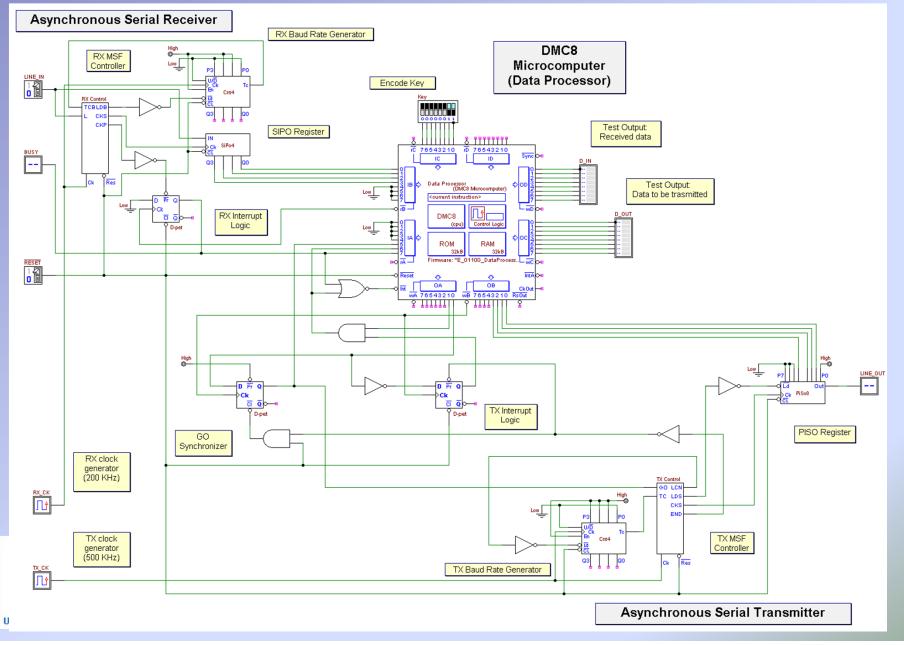

### The complete system

- The whole system is presented as schematic, divided into logical blocks.

- The *embedded microcomputer* (MC) links the receiver and trasmitter modules (**RX and TX**) and controls data flow.

- The interrupt logic block (IL) is a key element of the project

# DEEDS Laboratory Session - Mozilla Firefox Eile Modifica Visualizza Cronologia Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti ? Image: Segnalibri Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti Image: Segnalibri Image: Segnalibri Strumenti ? Image: Segnalibri Strumenti Image: Segnalibri Image: Segnalibri Image: Segnalibri Strumenti ? Image: Segnalibri Image: Segnalibri Image: Segnalibri Strumenti ? Image: Segnalibri Image: Segnalibri Image: Segnalibri Image: Segnalibri Strumenti Image: Segnalibri Image: Segnalibri Image: Segnalibri Image: Segnalibri Segnalibri Image: Segnalibri Image: Segnalibri Image: Segnalibri Image: Segnalibri Segnalibri Image: Segnalibri Image: Segnalibri Image: Segnalibri

In the next figure is represented the schematic of the whole system (click <u>here to enlarge the figure</u>, or click on the figure to <u>open the</u> <u>schematic</u> in the *d-DcS* editor):

This figure is quite complex, so we have marked, in red, four functional areas. The serial receiver [RX] and the transmitter [TX], that we analysed before, are clearly recognizable; likewise, the *DMC8 micro-computer* [MC]. The fourth area, that includes three flip-flops D-PET and some logic gates, is the interrupt logic [IL].

GOMS

electronic systems and net

Completato

### The receiver interrupt controller

- The text explains the purpose and operation of the receiver interrupt logic.

- The understanding of the interrupt controller logic behavior is essential for developing the micro-computer program

DEEDS Laboratory Session - Mozilla Firefox

Eile

Modifica

Visualizza

Cronologia

Segnalibri

Strumenti

?

O

C

X

A

Image: Construction of the strumenti

?

Image: Construction of the strumenti

?

O

C

X

A

Image: Construction of the strumenti

?

Image: Construction of the strumenti

?

In the following figure, a part of the circuit is highlighted. A D-PET flip-flop is set when the receiver activates CKP (signaling that a new data packet has been received). The output of the flip-flop (through a NOR logic gate) will interrupt the micro-computer, activating the line !Int. The same net is connected to **bit 7** of the IA input port, so that the interrupt handler routine could recognize the receiver as the device that requested interrupt. Moreover, the **!rB strobe** of the **IB port** is connected to the clock input of the **D-PET** flip-flop: when data is read on **IE port**, the flip-flop is automatically cleared and **the interrupt request cancelled**.

The transmitter interrupt logic is more complex. It is highlighted in the next figure, where the **D-PET** flip-flop on the left hand side serves as synchronizer for the GO command that start data transmission. Infact, when the micro-computer writes on **OB port** the data to be transmitted, the **!wB strobe** of the same port causes the flip-flop to load its **D input**, activating the GO command and starting data transmission (but only if transmitter interrupt has been enabled, through **OA port**).

111

Completato

electronic systems and networking group

### The transmitter interrupt controller

- The text continues with the explanation of the operation of the transmitter interrupt logic.

- This circuit is more complex than the previous one.

- The student learns how to deal with a programmable interrupt controller.

- A full understanding of the interrupt operation could be difficult at this stage.

The other **D-PET** flop-flop is clocked in same way, when **OB port** is written. However, this operation serves normally to clear the flip-flop. Infact the transmitter, when the transmission process terminates, activates the **END** signal that, in turn, sets the flip-flop, requesting interrupt to the micro-computer. The same request is connected to **bit 6** of the **IA input port**, so that the interrupt handler routine could recognize the transmitter as author of the request.

When interrupted by the transmitter, the micro-computer will send another byte to the **OB port** and this operation, at the same time: **a**) will start the transmission (activating **GO**), **b**) will clear the interrupt request; **c**) prepare the new interrupt request that will be generated on the end of transmission. **OA port** permits also to set the interrupt logic in a particulare mode that enables the generation of an interrupt request the first time we need to transmit data.

Completato

#### Symposium on Embedded Systems and Applications

electronic systems and networking group

dibe - university of genoa - italy

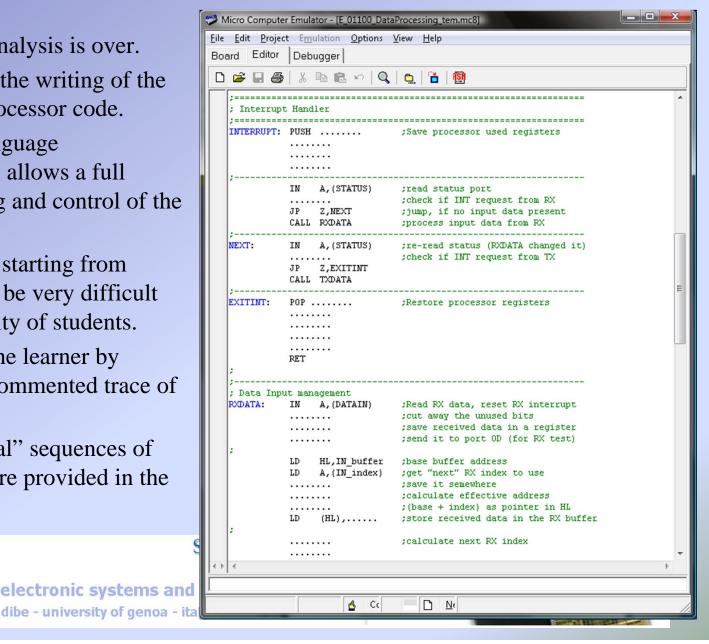

## **Programming the embedded processor (1)**

- The system analysis is over.

- Next stage is the writing of the embedded processor code.

- Assembly language programming allows a full understanding and control of the system.

- At this stage, starting from scratch could be very difficult for the majority of students.

- We support the learner by providing a commented trace of the program.

- A few "critical" sequences of instructions are provided in the trace.

University of Genoa

### **Programming the embedded processor (2)**

S

electronic systems and r

dibe - university of genoa - italy

- The finished program, coded following the given trace, must be *compiled and loaded* into the micro-computer memory.

- The completed system is now ready for testing.

| Micro Computer Emulator - [E_01100_DataProcessing_Sol.mc8] |                         |            |                          |                                                                |    |  |  |

|------------------------------------------------------------|-------------------------|------------|--------------------------|----------------------------------------------------------------|----|--|--|

| <u>File Edit Project Emulation Options View H</u> elp      |                         |            |                          |                                                                |    |  |  |

| Board Editor Debugger                                      |                         |            |                          |                                                                |    |  |  |

|                                                            |                         |            |                          |                                                                |    |  |  |

|                                                            | <b>~</b> • •            | 1          |                          | <u>c.</u>   <mark>`a</mark>   🕲                                |    |  |  |

|                                                            | ; ^                     |            |                          |                                                                |    |  |  |

|                                                            | ; Interrupt Handler     |            |                          |                                                                |    |  |  |

|                                                            | INTERRUPT:              |            | AF<br>BC                 | ;Save processor used registers                                 |    |  |  |

|                                                            |                         | PUSH       |                          |                                                                |    |  |  |

|                                                            | ;                       | IN         | A, (STATUS)              | ;read status port                                              |    |  |  |

|                                                            |                         | BIT        | 7,A                      | ; check if INT request from RX                                 |    |  |  |

|                                                            |                         |            | Z,NEXT<br>RXDATA         | ;jump, if no input data present<br>;process input data from RX |    |  |  |

|                                                            | NEXT:                   | IN         | A,(STATUS)               | ;re-read status (RXDATA changed it)                            |    |  |  |

|                                                            |                         | BIT<br>JP  | 6,A<br>Z,EXITINT         | ; check if INT request from TX                                 |    |  |  |

|                                                            |                         | CALL       | TXDATA                   |                                                                |    |  |  |

|                                                            | EXITINT:                | POP        | HL                       | Restore processor registers                                    |    |  |  |

|                                                            |                         | POP        | DE                       |                                                                | E  |  |  |

|                                                            |                         | POP<br>POP | BC<br>AF                 |                                                                |    |  |  |

|                                                            |                         | EI         |                          |                                                                |    |  |  |

|                                                            |                         | RET        |                          |                                                                |    |  |  |

|                                                            | ;                       |            |                          |                                                                |    |  |  |

|                                                            | ; Data Input management |            |                          |                                                                |    |  |  |

|                                                            | RXDATA:                 | IN<br>AND  | A, (DATAIN)<br>00001111b | Read RX data, reset RX interrupt;<br>cut away the unused bits  |    |  |  |

|                                                            |                         | LD         | C,A                      | ;save received data in C register                              |    |  |  |

|                                                            |                         | OUT        | (RXTEST),A               | ;send it to port OD (for RX test)                              |    |  |  |

|                                                            | ;                       |            |                          |                                                                |    |  |  |

|                                                            |                         | LD         | HL, IN_buffer            |                                                                |    |  |  |

|                                                            |                         | LD         | A,(IN_index)             | ;get "next" RX index to use                                    |    |  |  |

|                                                            |                         | LD<br>ADD  | D,A<br>A,L               | ;save it in D<br>;calculate effective address                  |    |  |  |

|                                                            |                         | LD         |                          | ;(base + index) as pointer in HL                               |    |  |  |

|                                                            |                         | LD         | L,A<br>(HL),C            | store data in the RX buffer                                    |    |  |  |

|                                                            | ;                       |            |                          |                                                                |    |  |  |

|                                                            |                         | LD<br>INC  | A,D                      | ;calculate next RX index                                       |    |  |  |

|                                                            |                         | CP         | A<br>maxcount            | ;check it against max count                                    |    |  |  |

|                                                            |                         | JP         | NZ,EXITRX                | ;lower than max, jump                                          |    |  |  |

|                                                            | ;                       |            |                          |                                                                | -  |  |  |

| < >                                                        | •                       |            |                          |                                                                | F. |  |  |

|                                                            |                         |            |                          |                                                                |    |  |  |

|                                                            |                         |            | 🔥 Cc                     |                                                                | /  |  |  |

| _                                                          |                         | -          |                          |                                                                |    |  |  |

45

### The complete embedded system under test

46

### Testing the system: timing diagram analysis

• The timing diagram analysis, in relation with CPU state and code execution

| 🗑 d-DcS - Timing Diagram - (Timing Interval Simulation mode) |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                              |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                              | 1                                                                                     | ,  3mS , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RESET                                                        |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| © Bata Proce                                                 |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                                                              |                                                                                       | Data Processor [E_01100_DataProcessing_Sol.mc8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| - Clock                                                      |                                                                                       | Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 0 Bin 7 |  |  |  |  |  |

|                                                              |                                                                                       | A 0 0 0 0 0 0 0 0 0 F 0 0 × 0 × 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| - IntA                                                       |                                                                                       | B D D D D D D D D D D D D D D D D D D D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |