|

|

|||||||||||||||||||||||

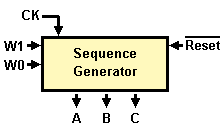

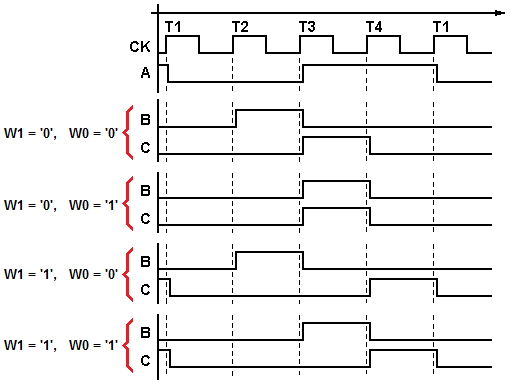

Design, using the Finite State Machine Simulator (d-FsM), a synchronous sequential network that generates several timing sequences on the outputs A, B and C, under control of the inputs W1 and W0: The basic sequence is cyclic over 4 clock cycles ( from T1 to T4). As shown in the timing diagram (see the next figure), the timings of the outputs B and C can be modified. They are activated for a single clock period, whose position is defined by the value of the inputs W1 e W0. The dependence of the outputs on inputs W1 and W0 can be represented also by the following table:

Suppose that inputs W1 and W0 are synchronous and could change their value only during the T1 cycle. The reset input (!Reset), when activated, will restart asynchronously the sequence from the T1 phase. The sequence generator must be designed in two versions: the first as a Moore type machine, the second as a Mealy one. It will be interesting to compare the two solutions, in terms of number of states and functionality. Download the d-FSM ASM diagram templates for the Moore and the Mealy versions. | ||||||||||||||||||||||||