|

|

|||||||||||||||||||||||

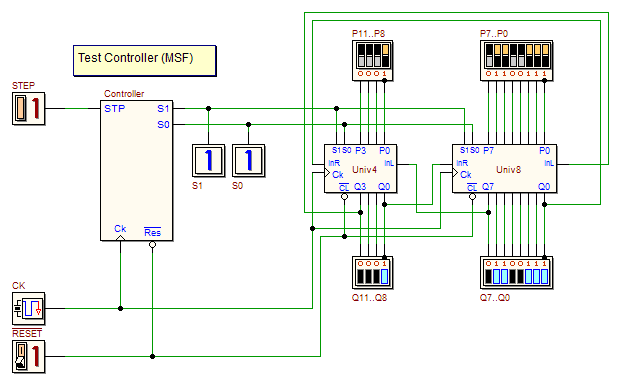

| In questo laboratorio si chiede di scrivere un programma, in assembly DMC8, che emuli un registro a scorrimento universale. Un registro di queesto tipo può operare sia in modo parallelo che seriale, in funzione degli ingressi di modo. Nello schema d-DcS che segue, utilizziamo i due registri Univ4 e Univ8, disponibili nella libreria di componenti del d-DcS. I due dispositivi sono connessi insieme a formare un unico registro a 12 bit. Il modo di lavoro del registro è controllato da un sequenziatore basato su MSF; il modo cambia quando il pulsante STEP è premuto (un click sulla figura aprirà lo schema nell'editor). L'impostazione del modo di lavoro dei registri universali Univ4 e Univ8 dipende dai valori degli ingressi S1 e S0, secondo la seguente tabella:

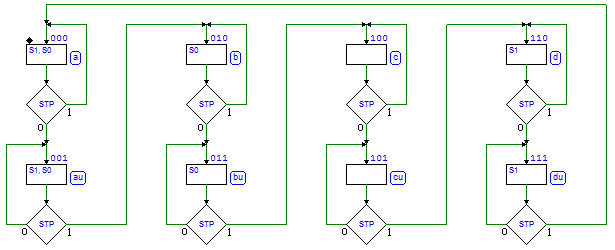

La funzionalità del controllore è descritta dal seguente diagramma ASM (un click sulla figura lo aprirà nel d-FsM): Al reset, il controllore forza il modo parallelo (S1='1', S0='1'): sul fronte di salita del clock, il valore presente agli ingressi P11..P0 è caricato nel registro a 12 bit e visualizzato dalle linee Q11..Q0. Alla pressione, e successivo rilascio, del pulsante STEP, il controllore cambia il modo del registro, in ordine ciclico: scorrimento a destra, modo di memorizzazione, scorrimento a sinistra, caricamento parallelo, e così via. Nello schema, i registri Univ4 e Univ8 sono connessi in modo circolare. Nella figura che segue, i percorsi dei segnali seriali sono evidenziati, per i casi di scorrimento a sinistra e a destra:

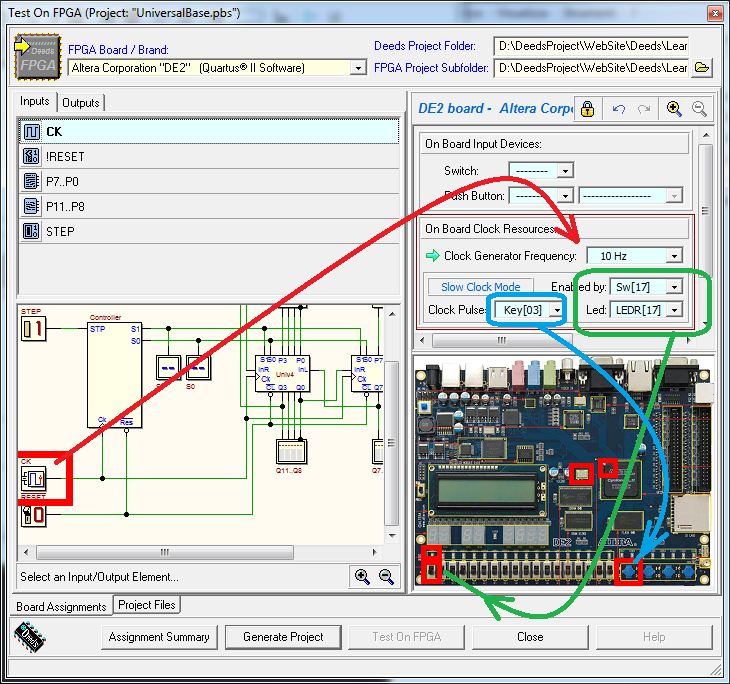

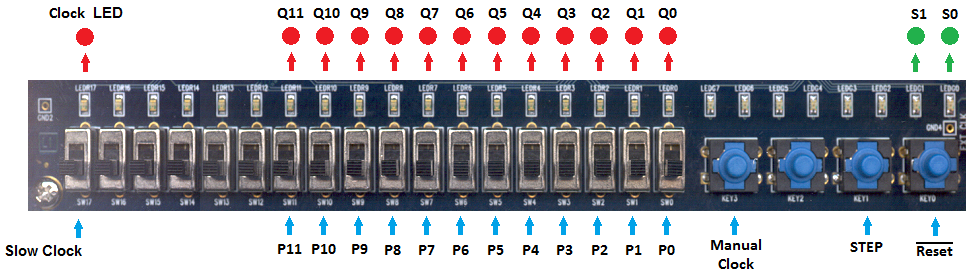

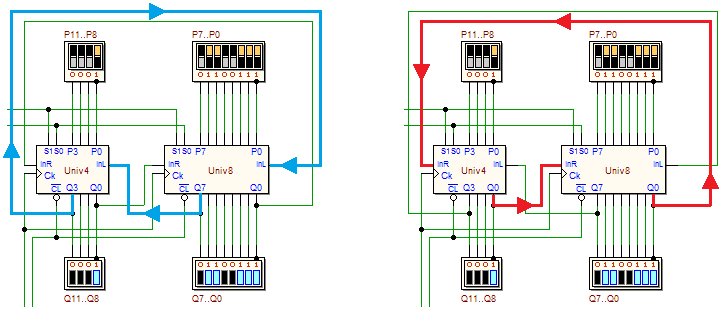

Quando il registro scorre verso sinistra (percorso evidenziato in blue), il bit più a sinistra di Univ4 (Q3) è riportato sul bit più a destra di Univ8 (attraverso il suo ingresso InL), mentre l'uscita Q7 di Univ8 è portata sul bit più a destra di Univ4. In modo speculare, quando il registro scorre verso destra (percorso evidenziato in rosso), sono utilizzate le uscite più a destra, connesse attraverso gli ingressi InR. Il circuito può essere testato con il d-DcS, in simulazione per animazione Il circuito può essere provato anche su di una scheda FPGA. La procedura generale è descritta passo passo nei tutorial introduttivi: Si apra la finestra "Test on FPGA" del d-DcS. Si noti che tutte le associazioni degli ingressi e uscite con i corrispondenti dispositivi della scheda FPGA sono state già predefinite, e non è necessario modificarle. Nella figura qui sotto, è evidenziata la predisposizione del clock.

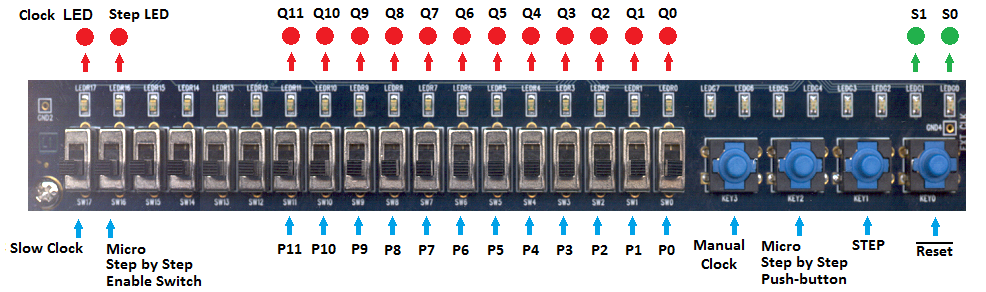

La frequenza del clock è stata impostata a 10 Hz (invece che a 10 KHz come nella simulazione), per premettere l'esame visivo del funzionamento del registro. E' stata anche scelta la modalità "Slow Clock Mode", assegnando all'interruttore Sw[17] il compito di attivarla al run time. E' stato anche selezionato un LED, il LEDR[17], al fine di visualizzare gli impulsi di clock inviati al circuito. Infine, il pulsante Key[03] è stato scelto per la generazione manuale degli impulsi di clock. Le associazioni sono evidenziate in modo riassuntivo nella figura seguente (il "pannello di controllo" del nostro sistema):

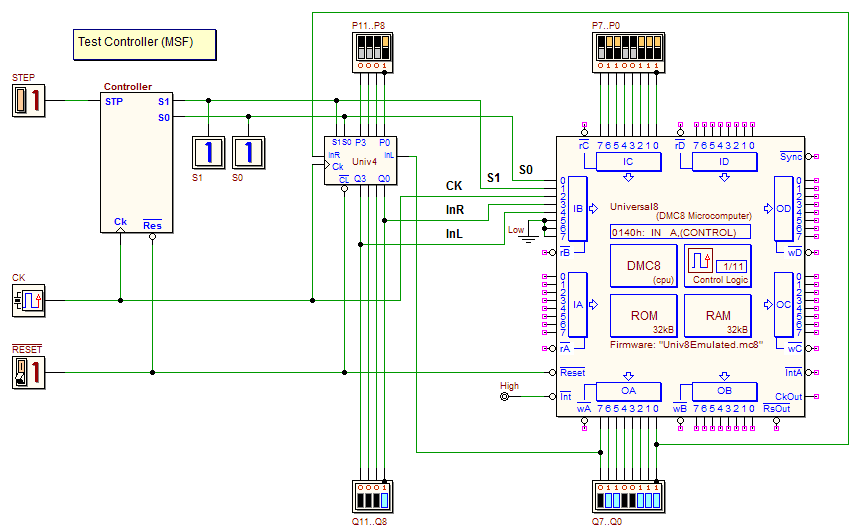

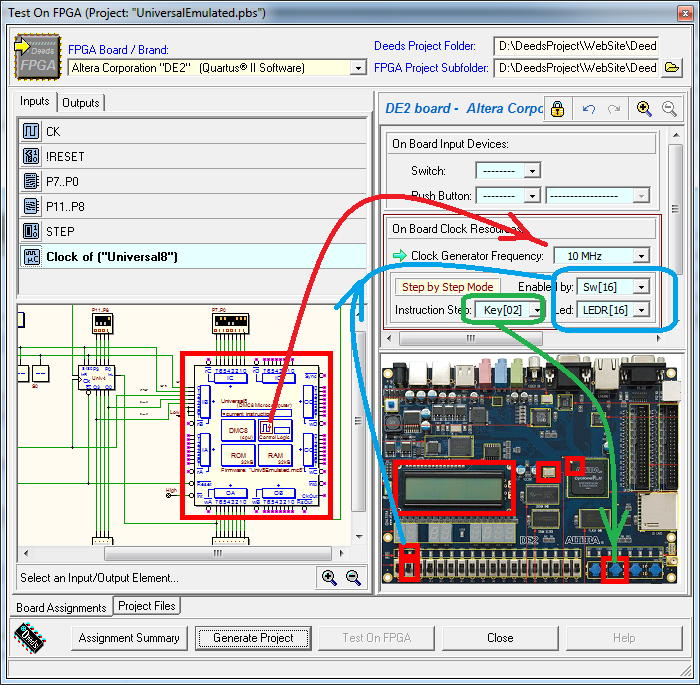

Dopo avere finito il test della rete, si consideri ora il nuovo circuito, mostrato nelle figura qui sotto, dove il componente Univ8 è stato sostituito, piedino per piedino, da un microcomputer che lo emulerà (il registro Univ4 è stato invece lasciato al suo posto). Si richiede di scrivere un programma in assembly DMC8 che riproduca dal punto di vista funzionale il componente Univ8 (un click sulla figura aprirà lo schema nel d-DcS). Come si vede in figura, utilizziamo il porto IC per collegare le linee P7..P0, il porto OA per generare le uscite Q7..Q0, e il porto IB per tutti gli altri ingressi (S0, S1, CK, InR, InL). La frequenza di clock del microcomputer è 10 MHz; per ottenere una ragionevole emulazione del registro, la frequenza del clock CK deve essere molto più bassa. Per questo motivo, nello schema il clock CK è impostato a 10 KHz (la frequenza utilizzata nella simulazione del precedente circuito). Si raccomanda di non apportare modifiche alle terminazioni di ingresso e uscita, che sono state preimpostate per il prossimo passo: l'esportazione del progetto su di una scheda FPGA. Qui è disponibile una traccia della soluzione, da completare. Conclusa la scrittura e i test preliminari del programma nel d-McE, lo si carichi nella ROM del microcomputer. Si verifichi il funzionamento della rete nel d-DcS, in simulazione per animazione Si passi alla realizzazione del prototipo del circuito sulla scheda FPGA, aprendo la finestra "Test on FPGA" del d-DcS: nella figura qui sotto, è selezionata la definizione del clock e del debugger del microcomputer.

La frequenza di clock è stata definita pari a 10 MHz. E' stata predisposta la modalità di esecuzione passo-passo ("Step by Step Mode"), assegnando l'interruttore Sw[16] al compito di abilitare (al "run time") tale funzione. E' stato predisposto un LED, il LEDR[16], come visualizzatore degli impulsi di clock che saranno inviati al microcomputer. Infine, è stato scelto il pulsante Key[02] come comando manuale dell'avanzamento delle istruzioni. Se l'interruttore Sw[16] è posto a '0', la funzione di debug non è attiva e il microcomputer funziona con il clock "normale" (10 MHz). Se l'interruttore Sw[16] è a '1', il clock del processore è inibito, e il sistema di debug resta in attesa che l'utente prema il pulsante Key[02] (a ogni pressione del pulsante, il microcomputer esegue una istruzione). Si noti che la definizione del clock del microcomputer non sostituisce quella del clock del circuito, che continua ad essere definito come nel precedente circuito, dal momento che si tratta di due definizioni separate. Anche in questo caso, la sua frequenza è definita pari a 10 Hz (per permettere l'analisi visiva del circuito). Anche la modalità "Slow Clock Mode" è stata mantenuta, assegnando ad essa l'interruttore Sw[17], il LED LEDR[17] e il pulsante Key[03] per la generazione manuale degli impulsi. La figura seguente, che riporta in modo riassuntivo le associazioni effettuate, è utile per il test del prototipo:

| ||||||||||||||||||||||||

e in simulazione temporale

e in simulazione temporale  (una opportuna sequenza di test è disponibile nella finestra del diagramma temporale).

(una opportuna sequenza di test è disponibile nella finestra del diagramma temporale).