Introduzione ai componenti FPGA e alla progettazione mediante HDL

9.1 FPGA (Field Programmable Gate Arrays)

9.1.8 Deeds e il supporto per i componenti FPGA

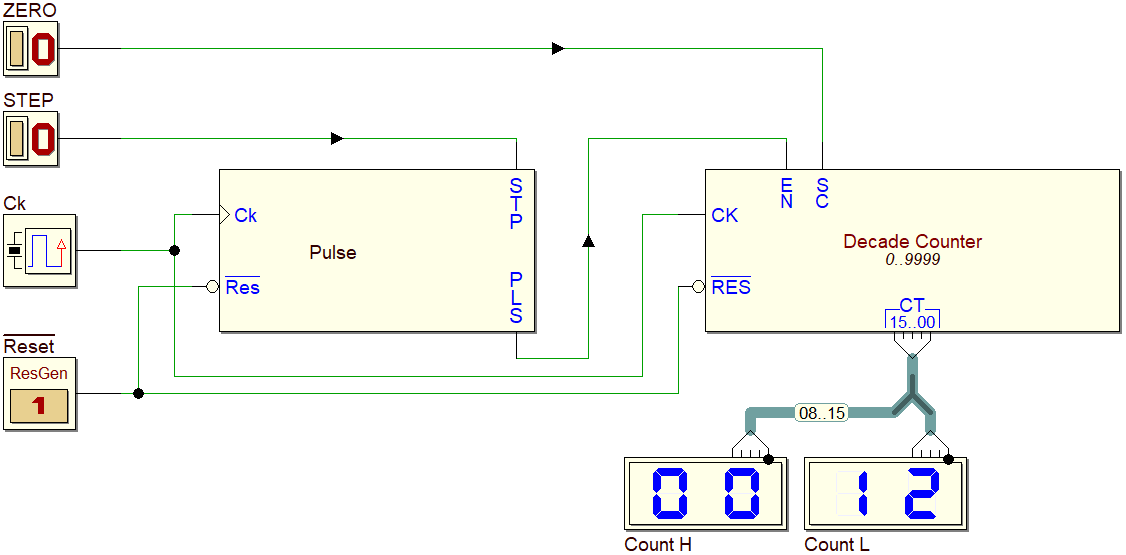

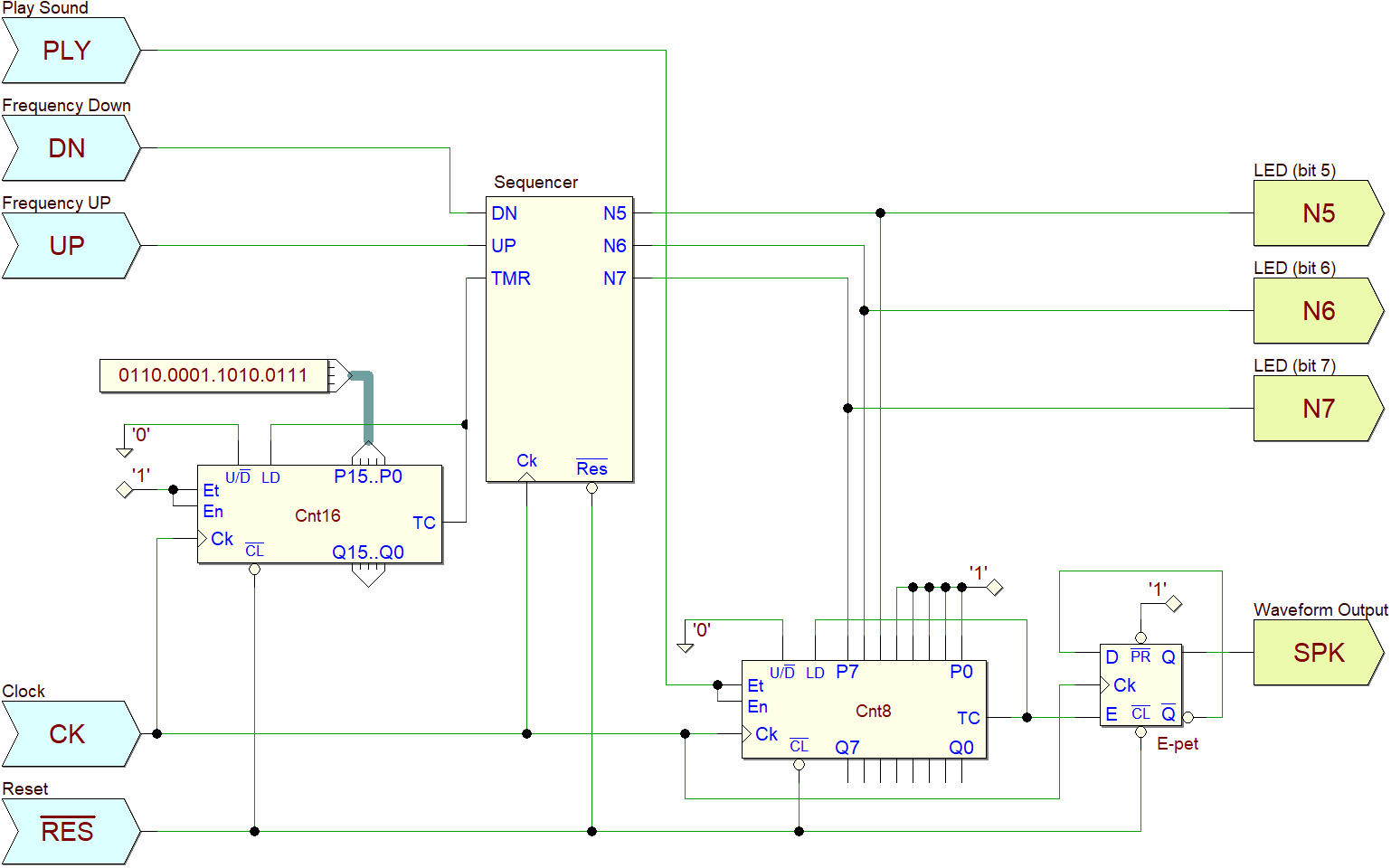

Schema del generatore di impulso (non ancora configurato per la FPGA)

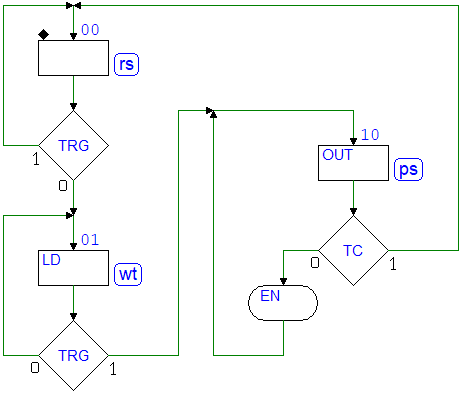

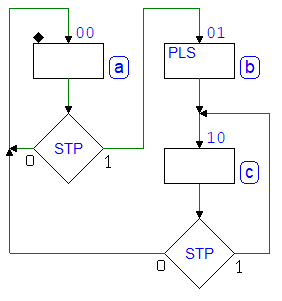

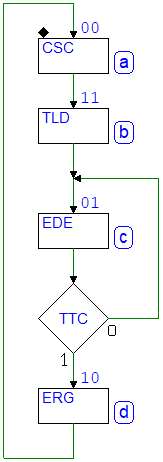

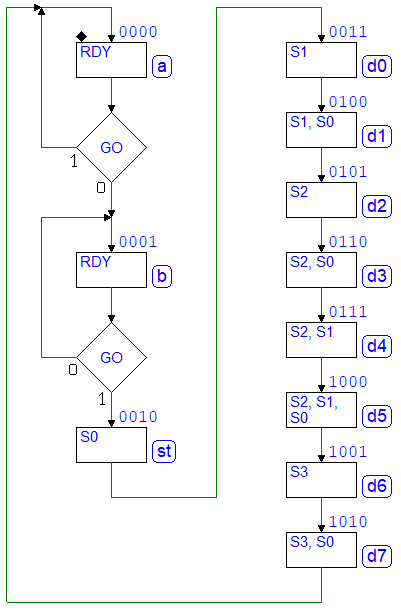

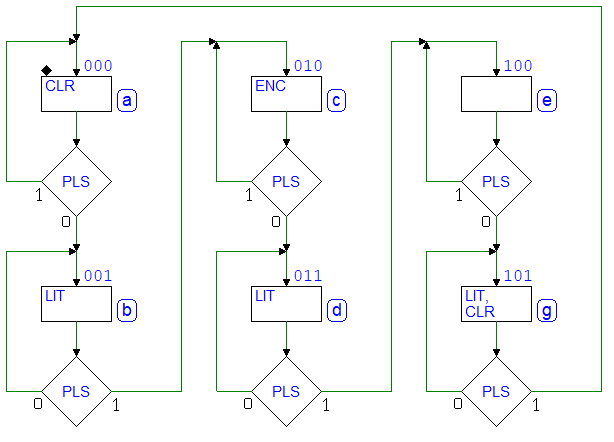

Esempio del generatore di impulso: diagramma ASM del controllore

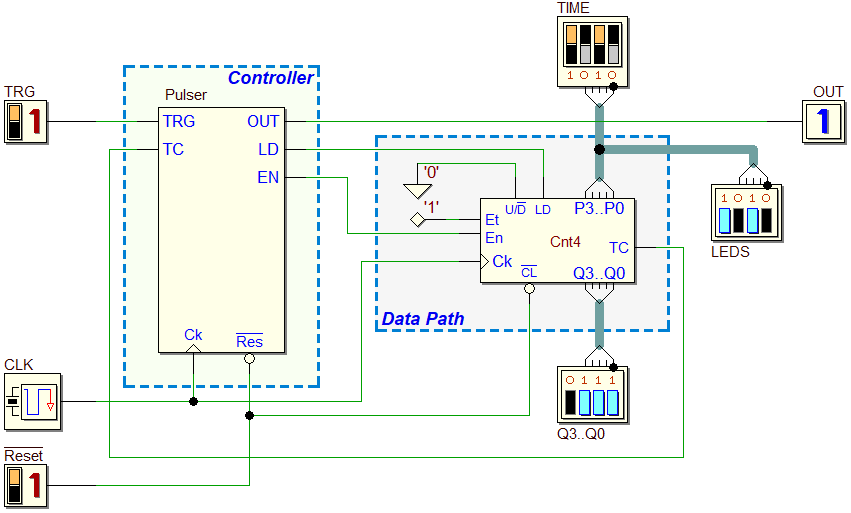

Schema del generatore di impulso (configurato per la FPGA)

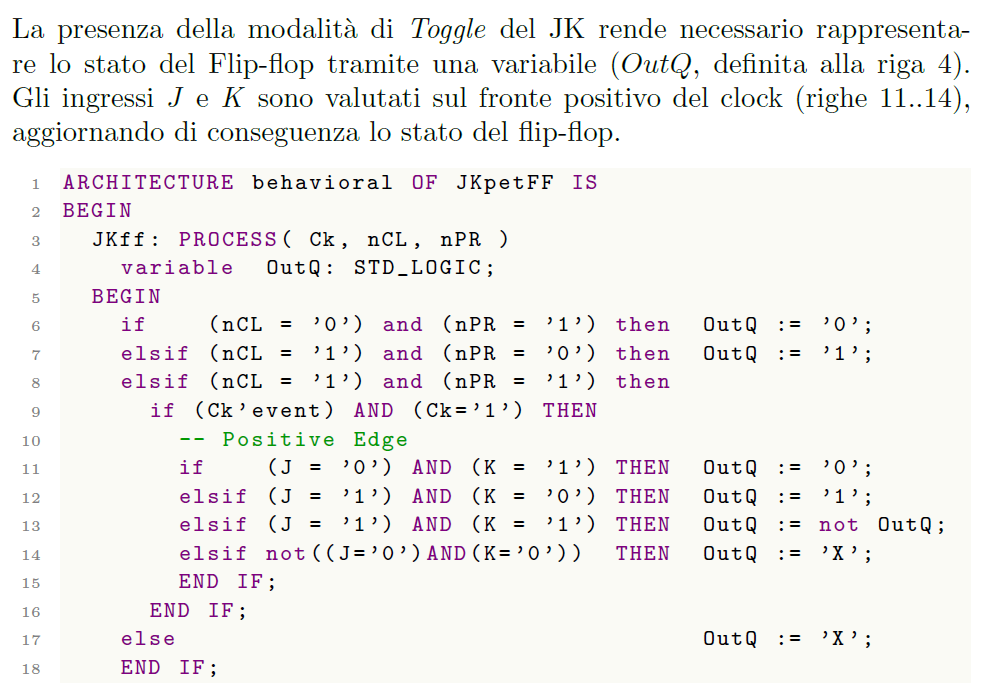

9.2 Introduzione al VHDL

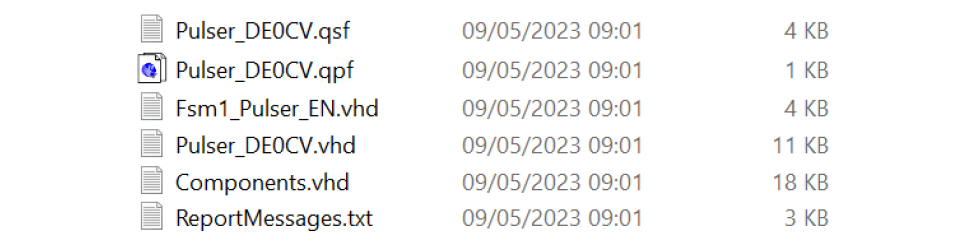

9.2.1 Il codice VHDL generato da Deeds

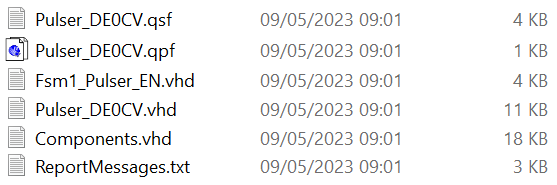

Un click sull'elenco sottostante permette di scaricare i file del progetto (generati da Deeds), come descritto nel capitolo):

9.3 Esercizi di prototipazione su FPGA

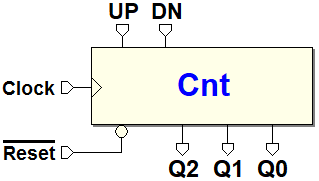

9.3.1 Contatore binario avanti-indietro non ciclico, a tre bit

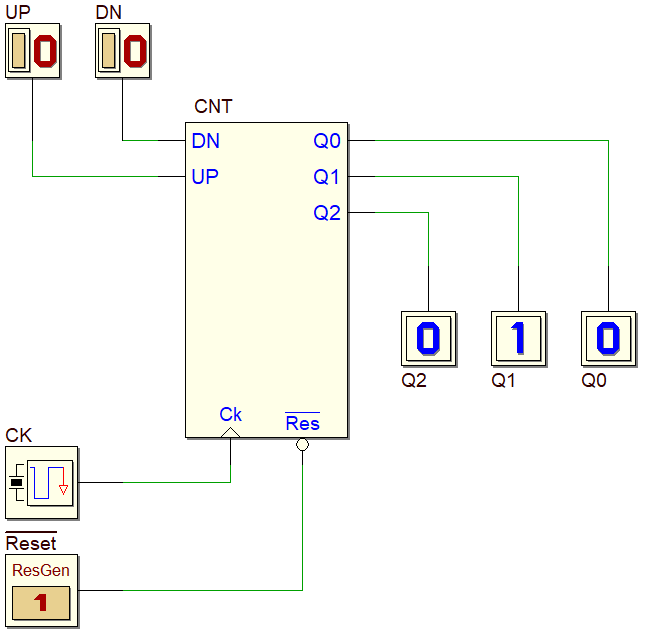

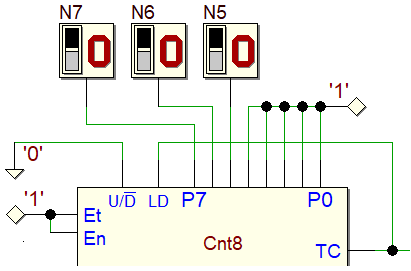

Traccia dello schema, da completare (senza MSF, e privo della configurazione FPGA):

Traccia dello schema, da completare (senza MSF, ma configurato per la FPGA):

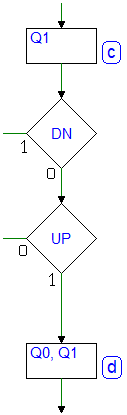

Traccia della MSF, da completare:

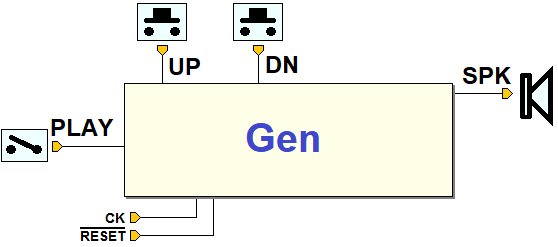

9.3.2 Generatore digitale di toni

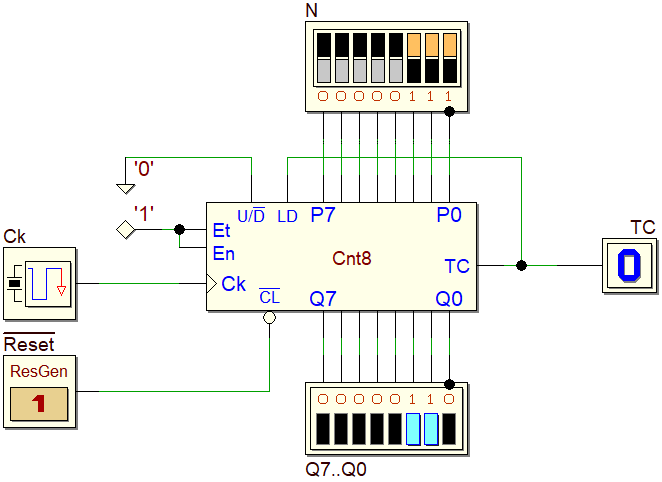

Esempio di rete per generare digitalmente un segnale periodico:

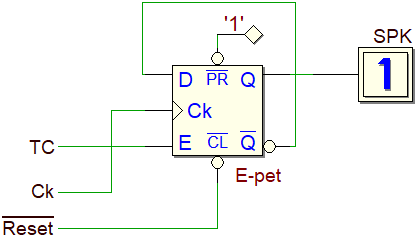

La stessa rete, con l'aggiunta del flip-flop visibile nella figura seguente, al fine di generare un segnale periodico con rapporto pieno vuoto pari al 50%:

La stessa rete, ulteriormente modificata con l'aggiunta dei controlli della frequenza (visibili nella figura seguente):

Traccia da completare della rete per la gestione dei pulsanti ed il controllo della frequenza:

Traccia da completare della MSF per la gestione dei pulsanti:

Traccia da completare della rete complessiva del generatore:

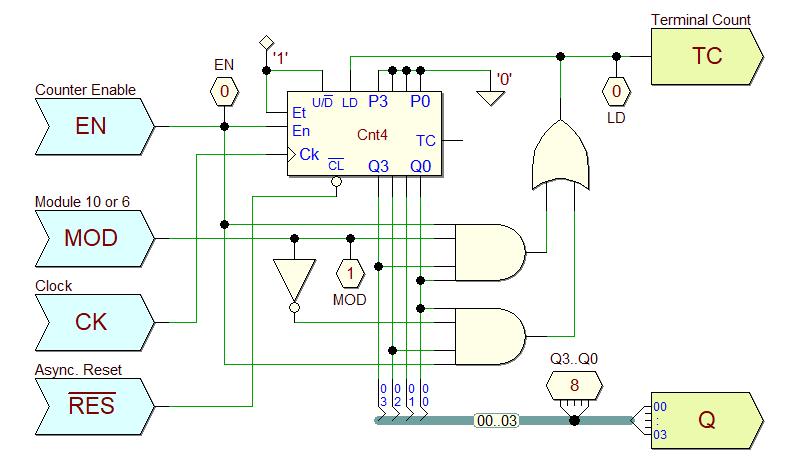

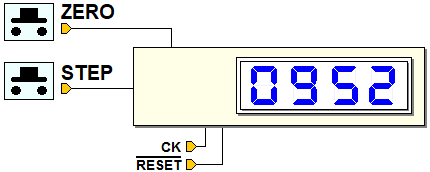

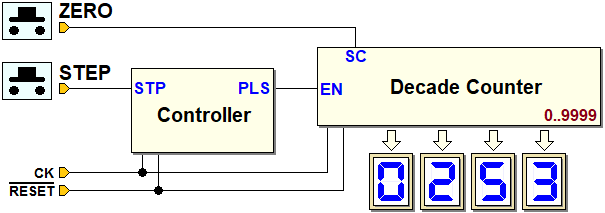

9.3.3 Contatore di eventi

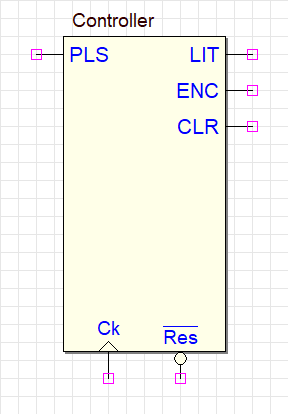

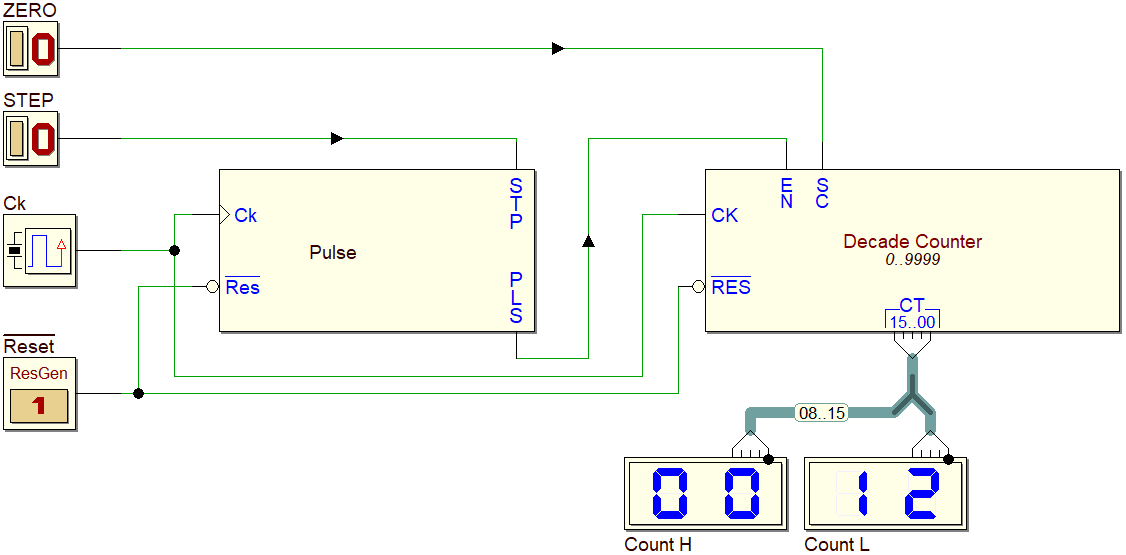

Schema a blocchi suggerito (Controller - Data Path):

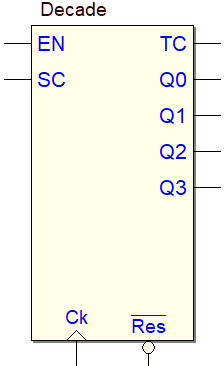

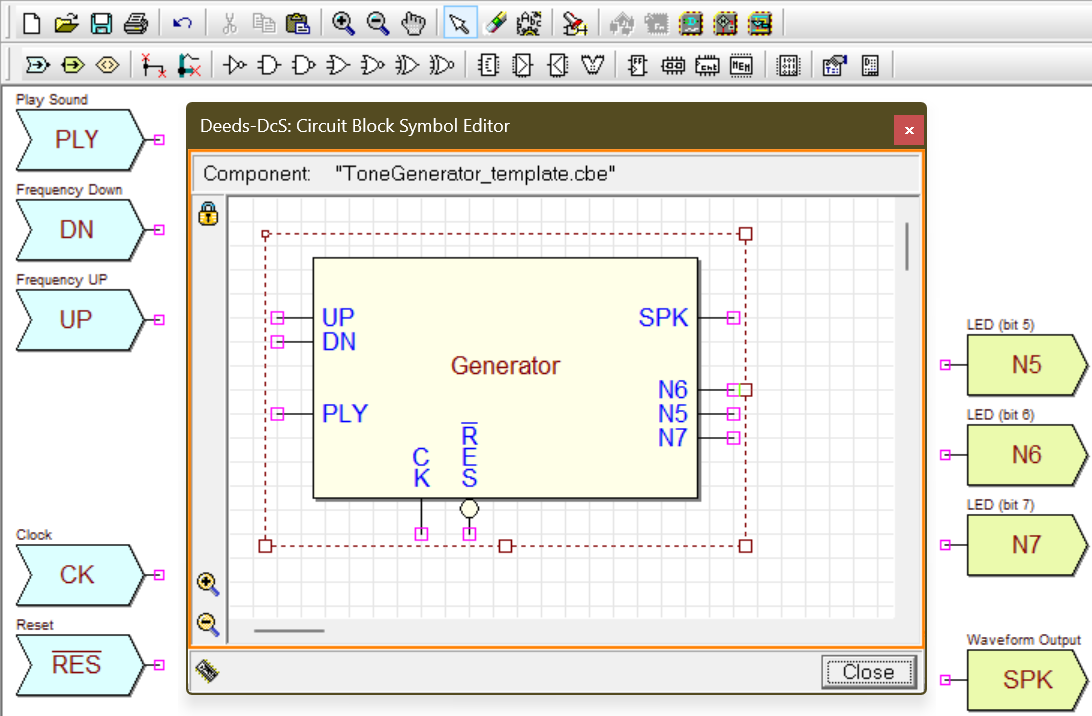

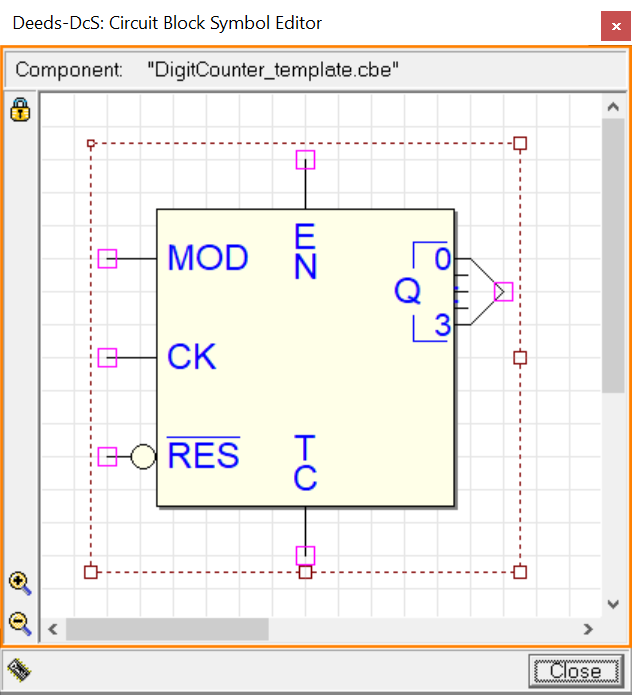

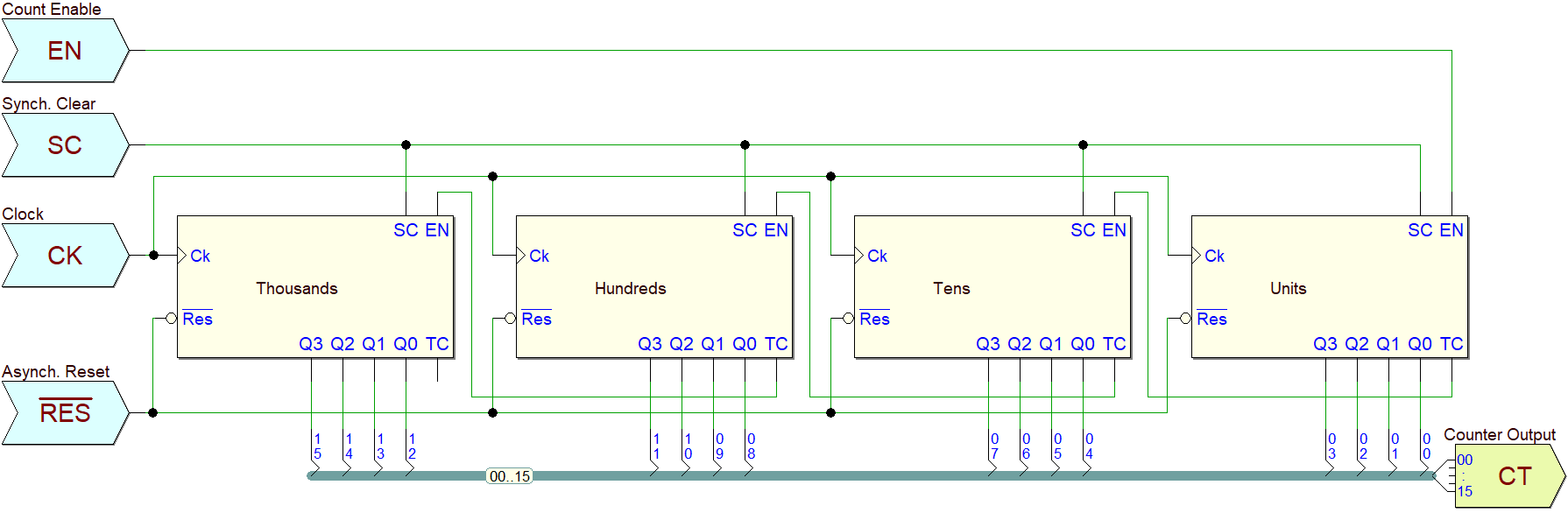

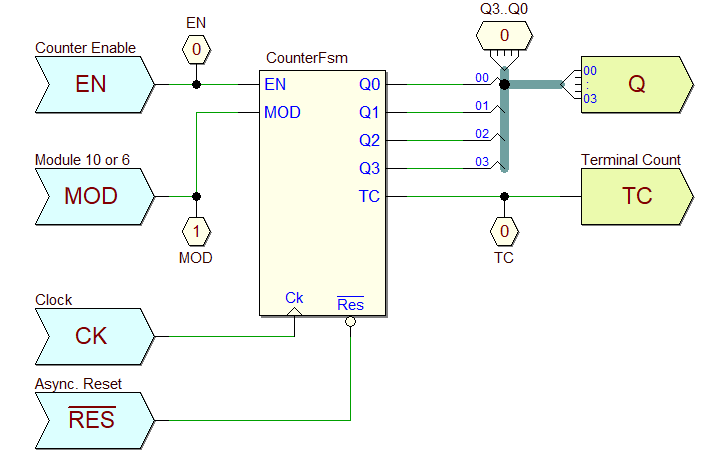

Esempio introduttivo alla creazione di un componente CBE (dopo avere aperto lo schema nel Deeds-DcS, premere "F7" per aprire l'Editor del Simbolo):

Traccia da completare del CBE contenente la rete del contatore dacadico (dopo avere aperto lo schema nel Deeds-DcS, premere "F7" per aprire l'Editor del Simbolo):

Traccia da completare della MSF che realizza il singolo modulo di conteggio in codice BCD:

Traccia da completare della rete complessiva del contatore di eventi:

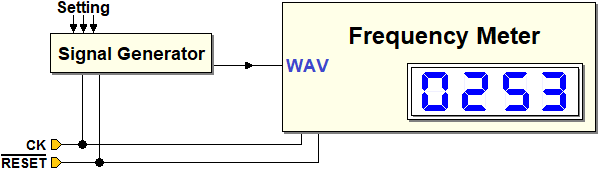

9.3.4 Frequenzimetro

Schema a blocchi della parte di conteggio e visualizzazione (facendo click si aprirà la traccia del CBE contenente il contatore decadico, lo stesso dell'esercizio precedente):

Traccia da completare della MSF che realizza il singolo modulo di conteggio in codice BCD (lo stesso dell'esercizio precedente):

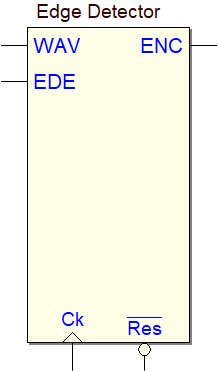

Traccia da completare della MSF del rilevatore dei fronti di salita del segnale da misurare:

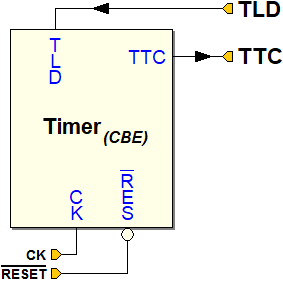

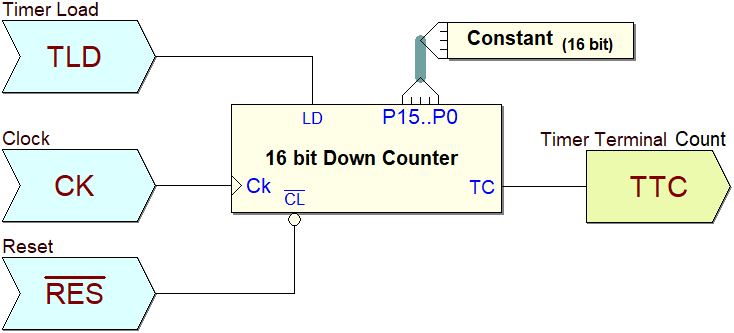

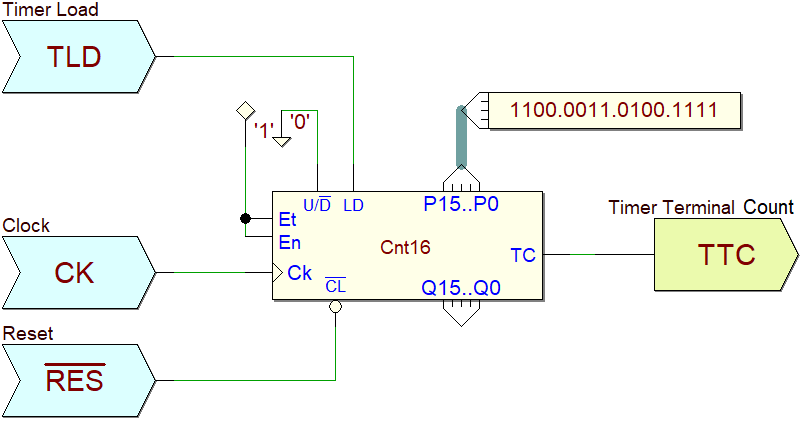

Schema del CBE contenente il timer, come proposto nel libro:

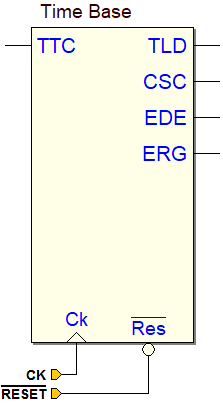

Traccia da completare della MSF della base dei tempi per la misura:

Traccia da completare del CBE che deve contenenere la rete del generatore (proposto nell'esercizio 9.3.2):

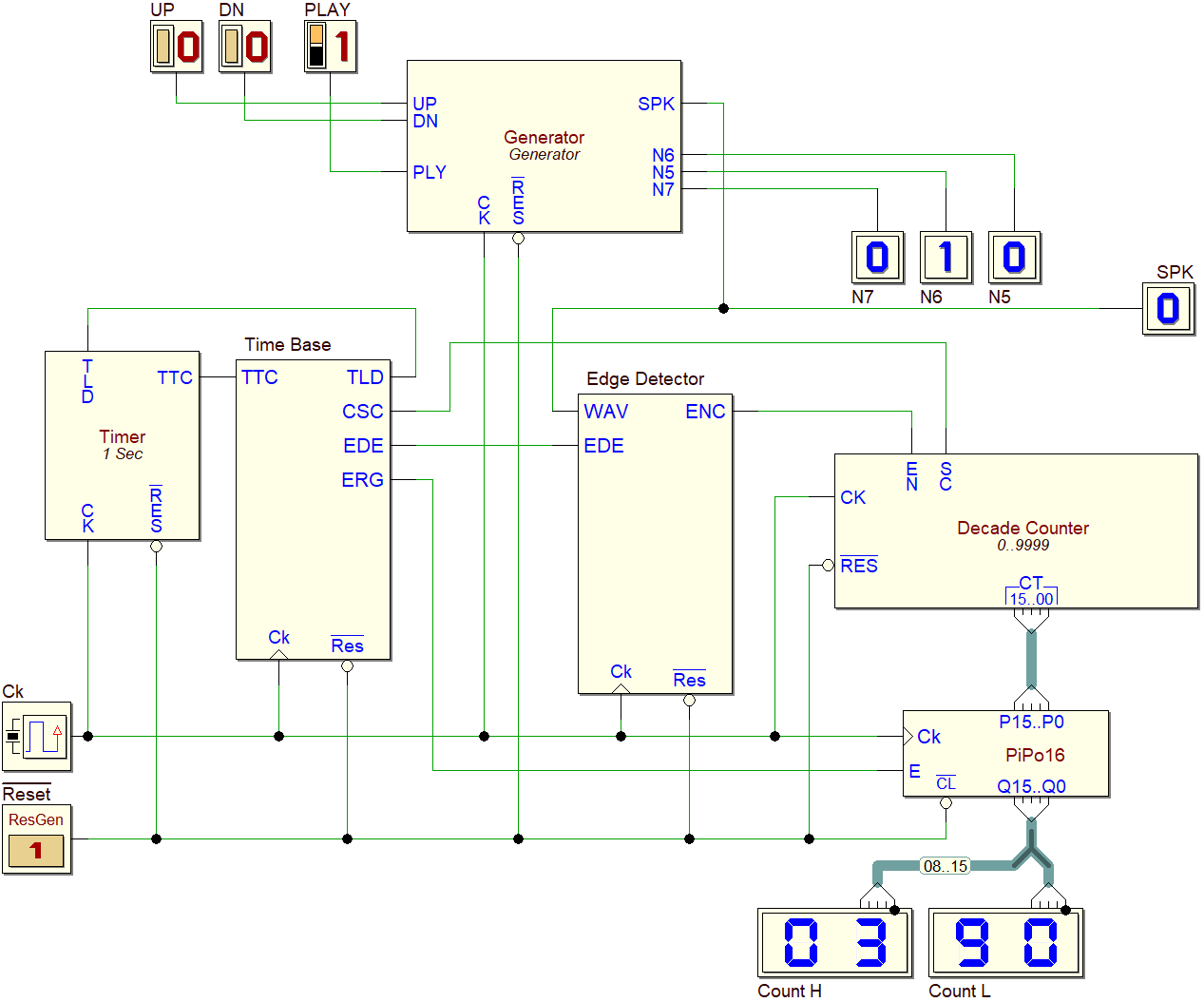

Traccia da completare della rete complessiva del frequenzimetro:

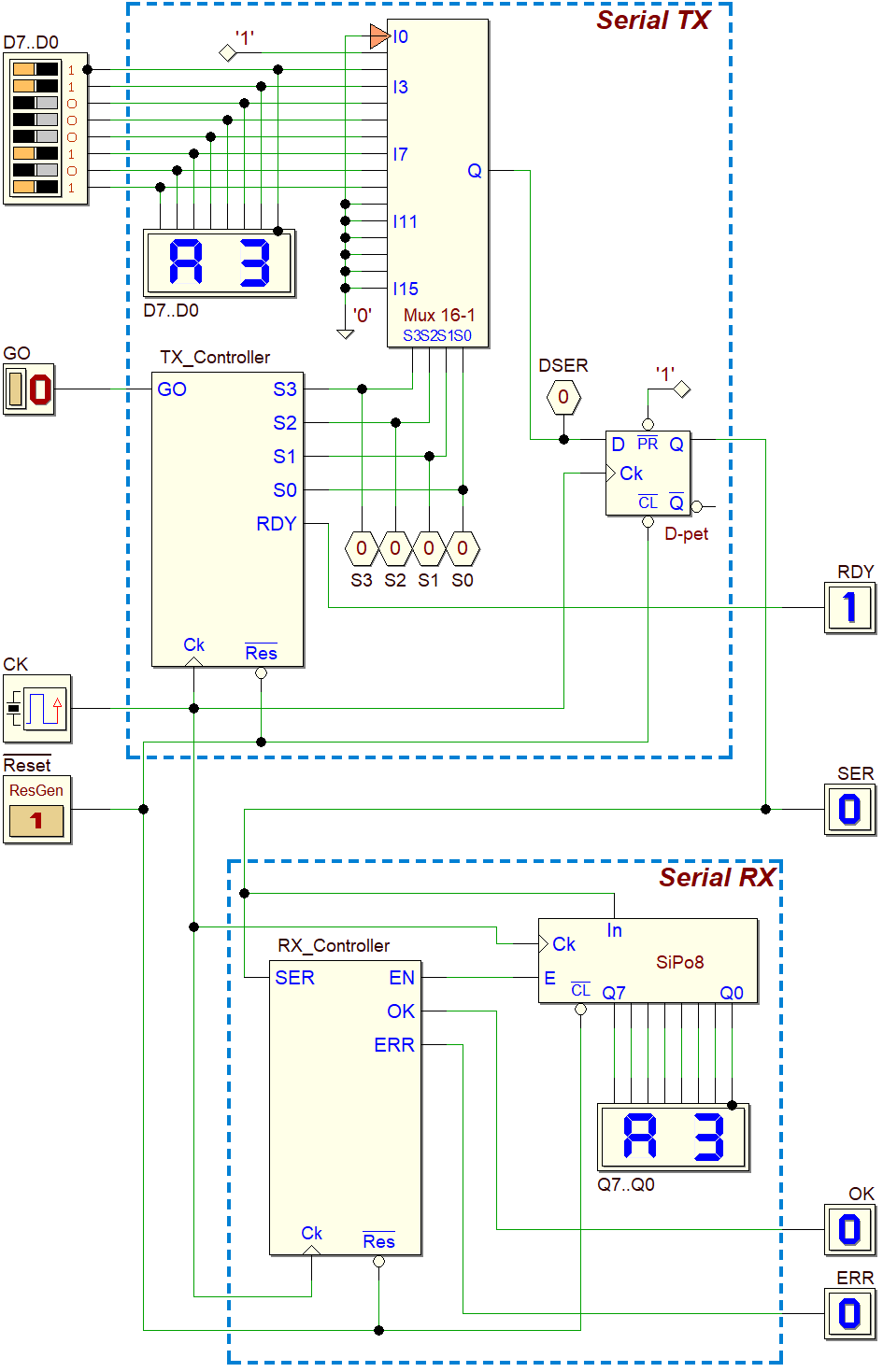

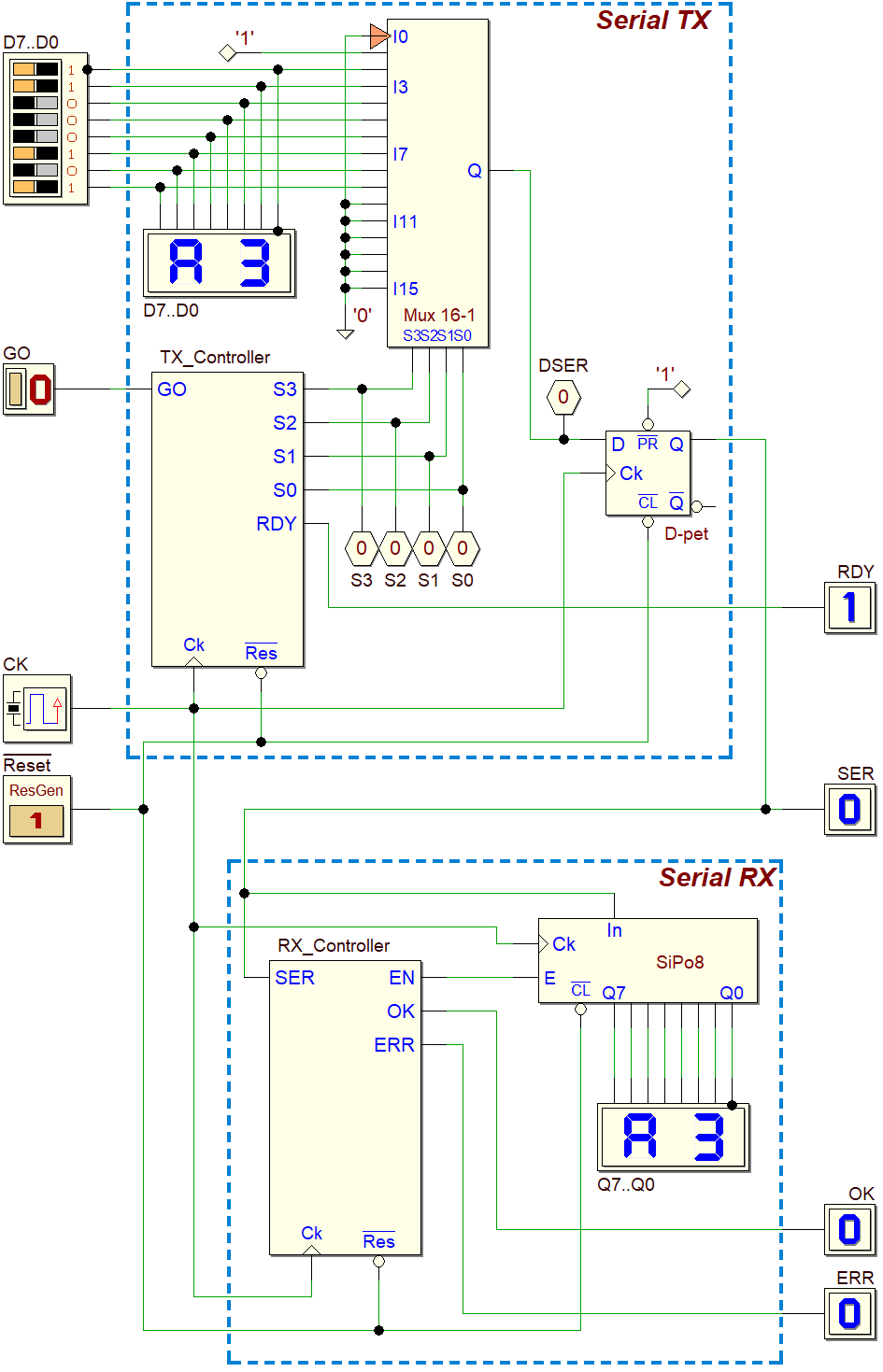

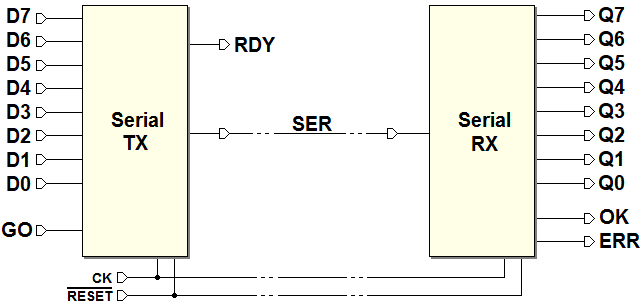

9.3.5 Sistema di comunicazione seriale sincrona (8 bit)

Traccia dello schema, da completare (senza MSF, e privo della configurazione FPGA):

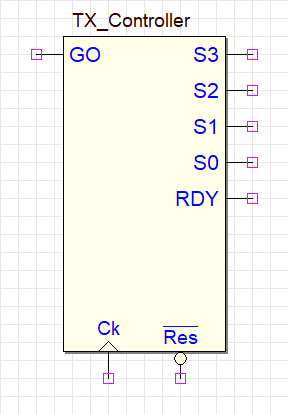

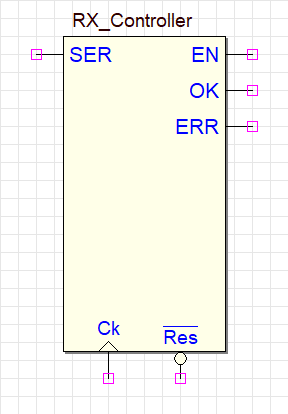

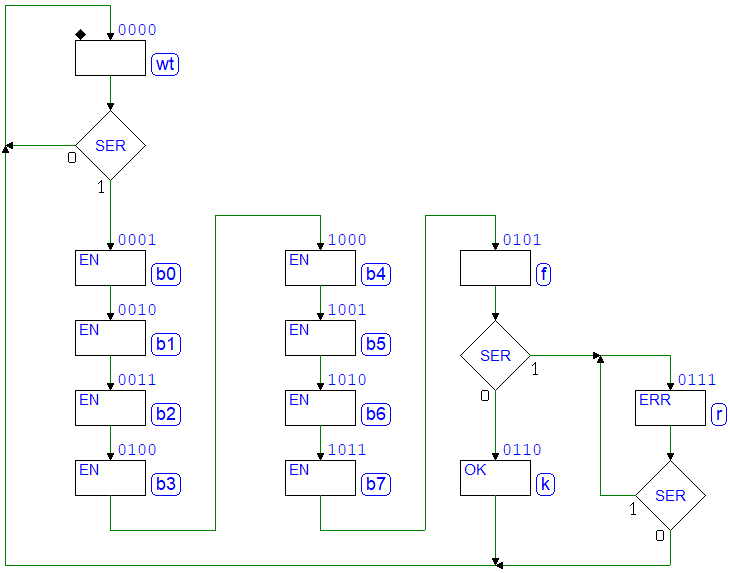

Tracce da completare delle MSF dei controllori del trasmettitore e del ricevitore:

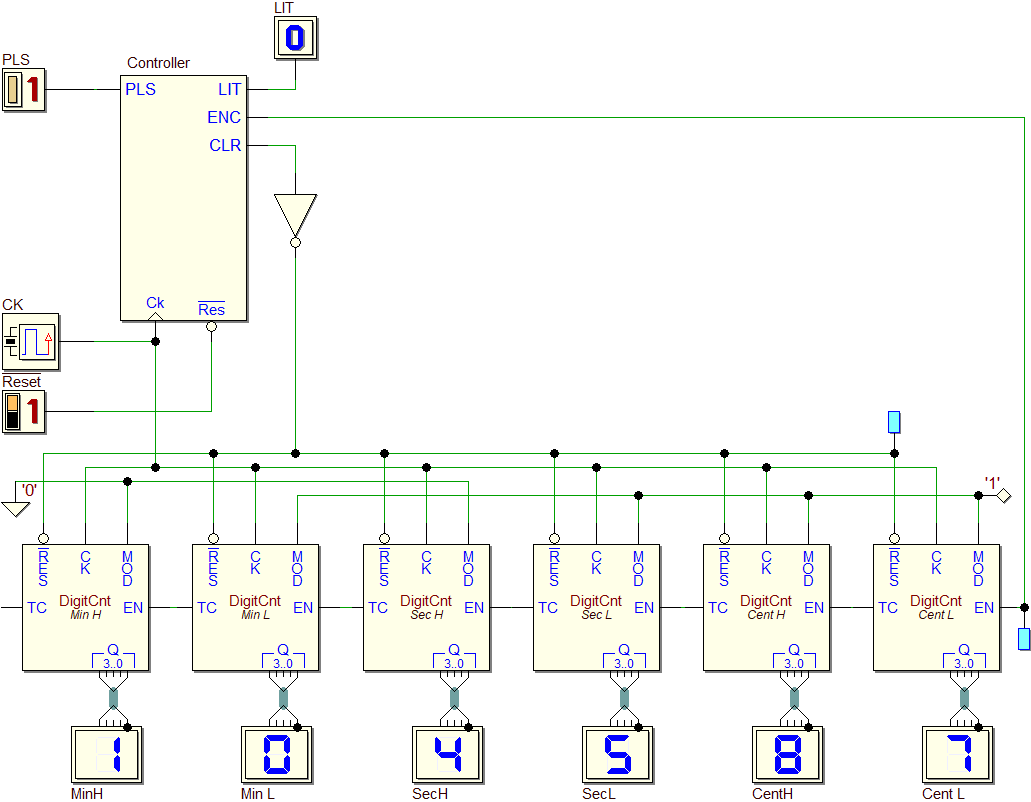

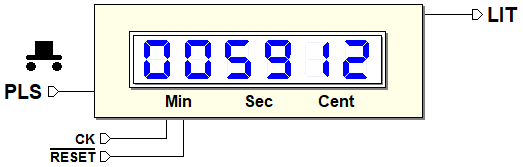

9.3.6 Cronometro digitale

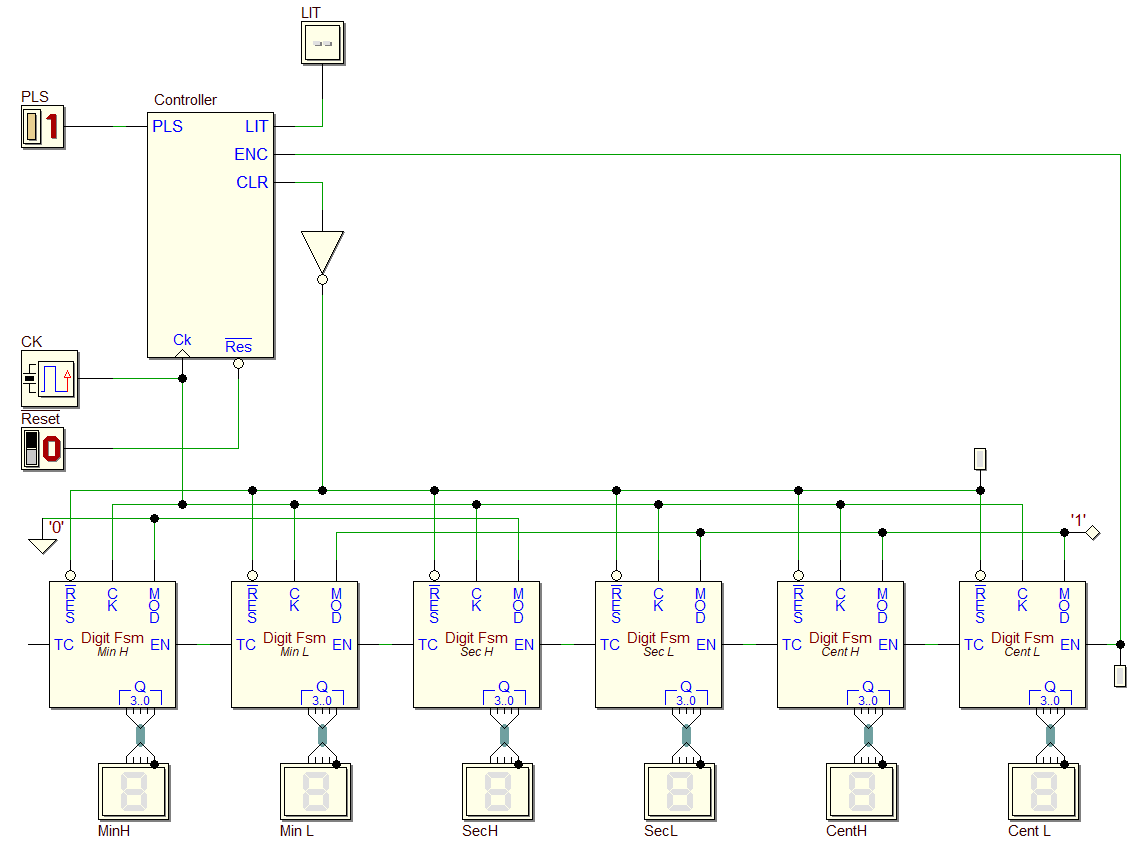

Traccia dello schema, da completare (senza MSF, e privo della configurazione FPGA):

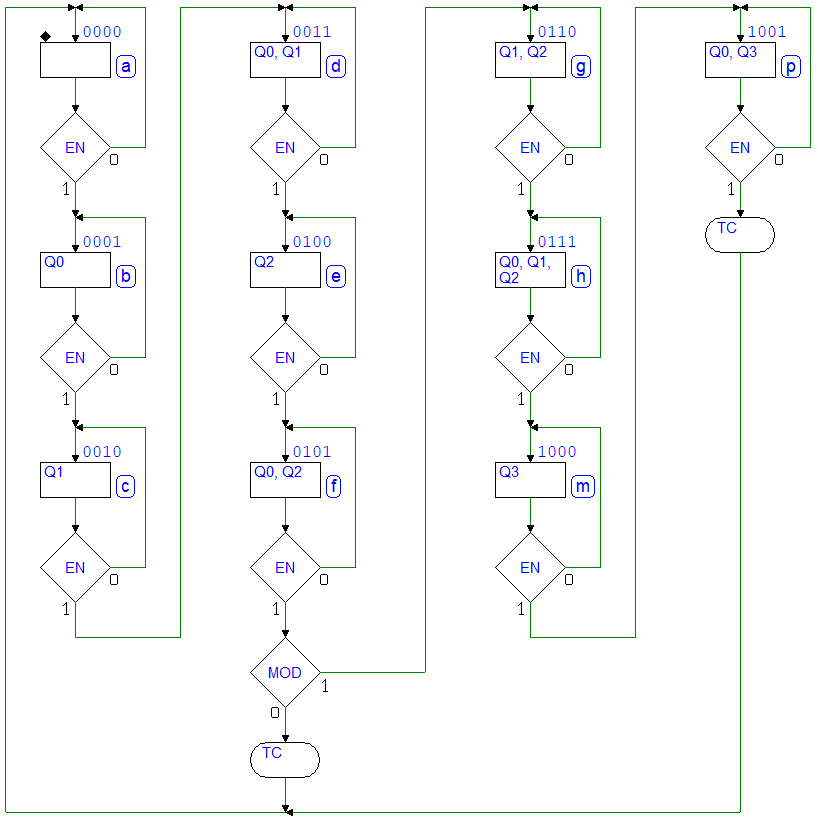

Traccia da completare della MSF del controllore:

Traccia da completare del CBE di un modulo del contatore decadico:

9.4 Soluzioni

9.4.1 Contatore binario avanti-indietro non ciclico, a tre bit

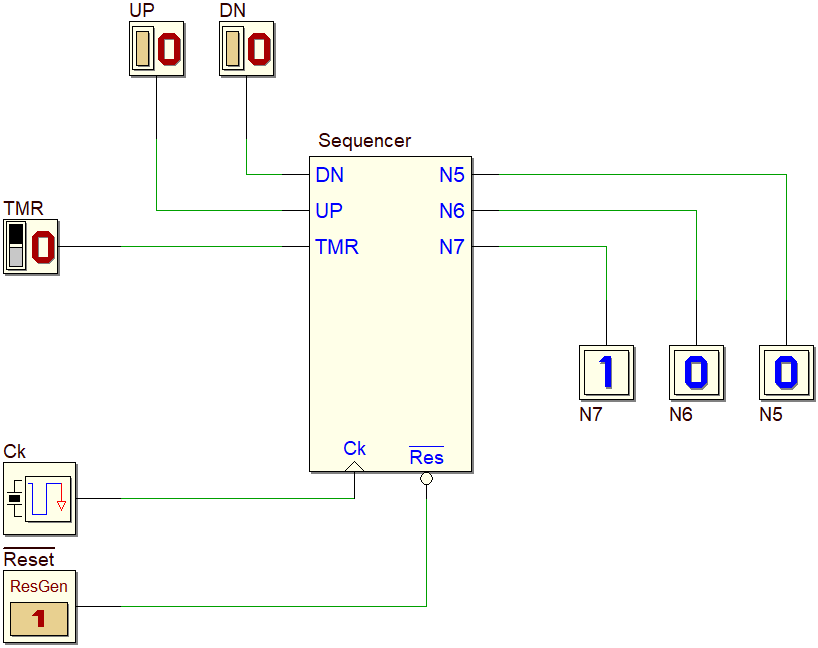

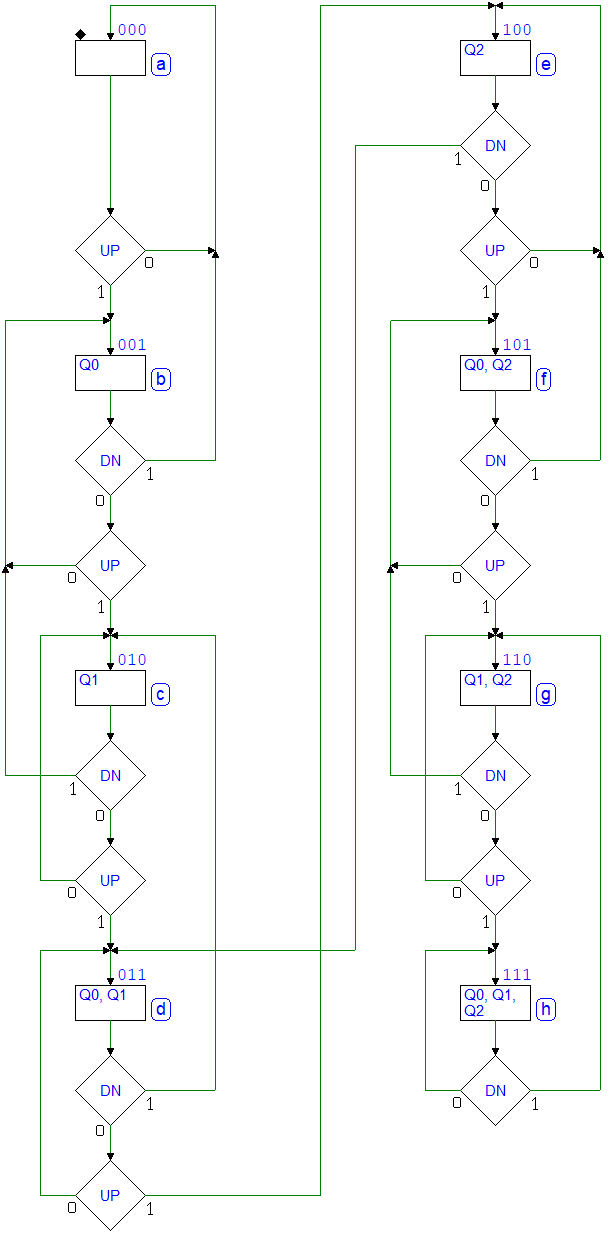

Diagramma ASM del contatore:

9.4.2 Generatore digitale di toni

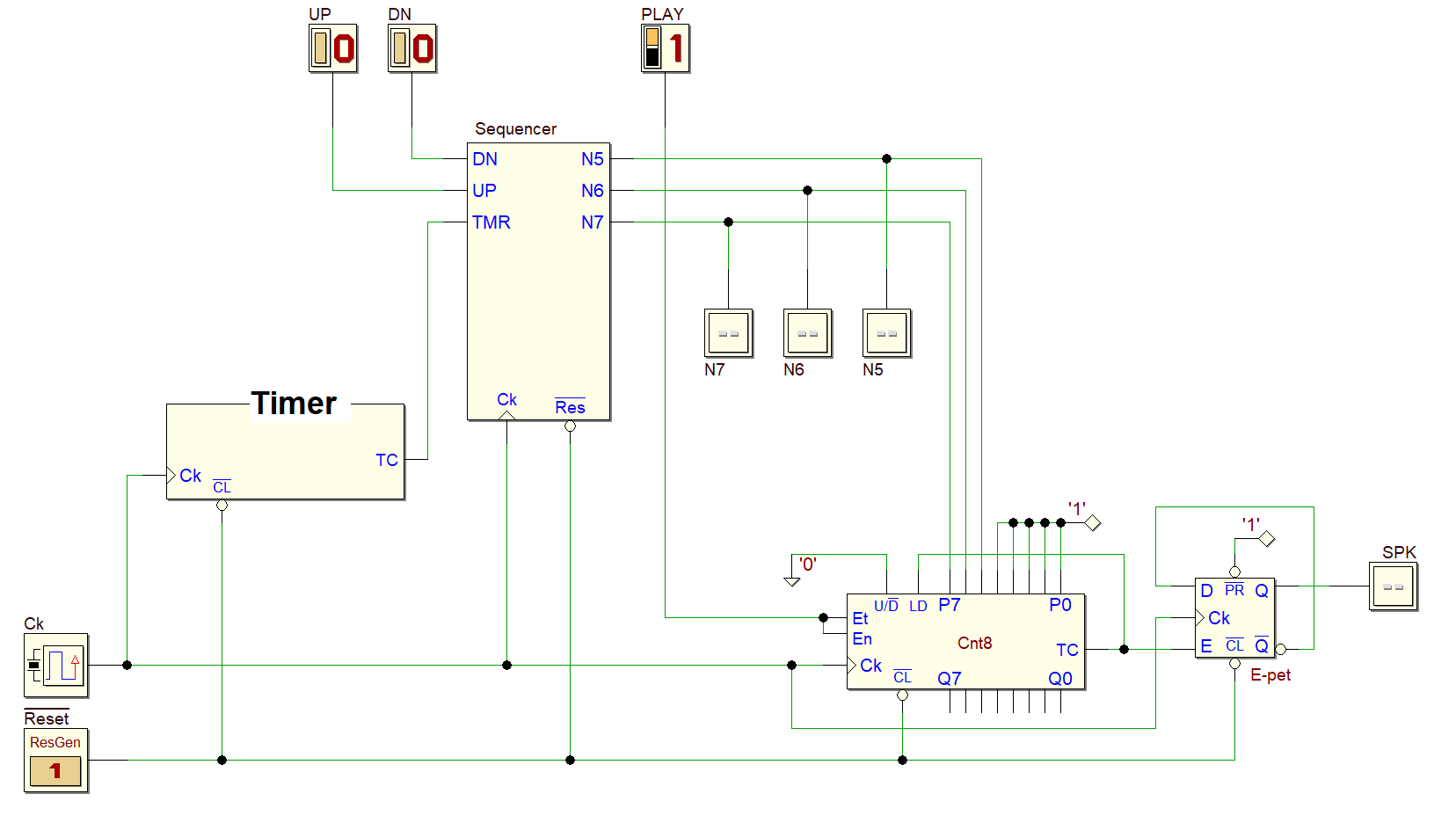

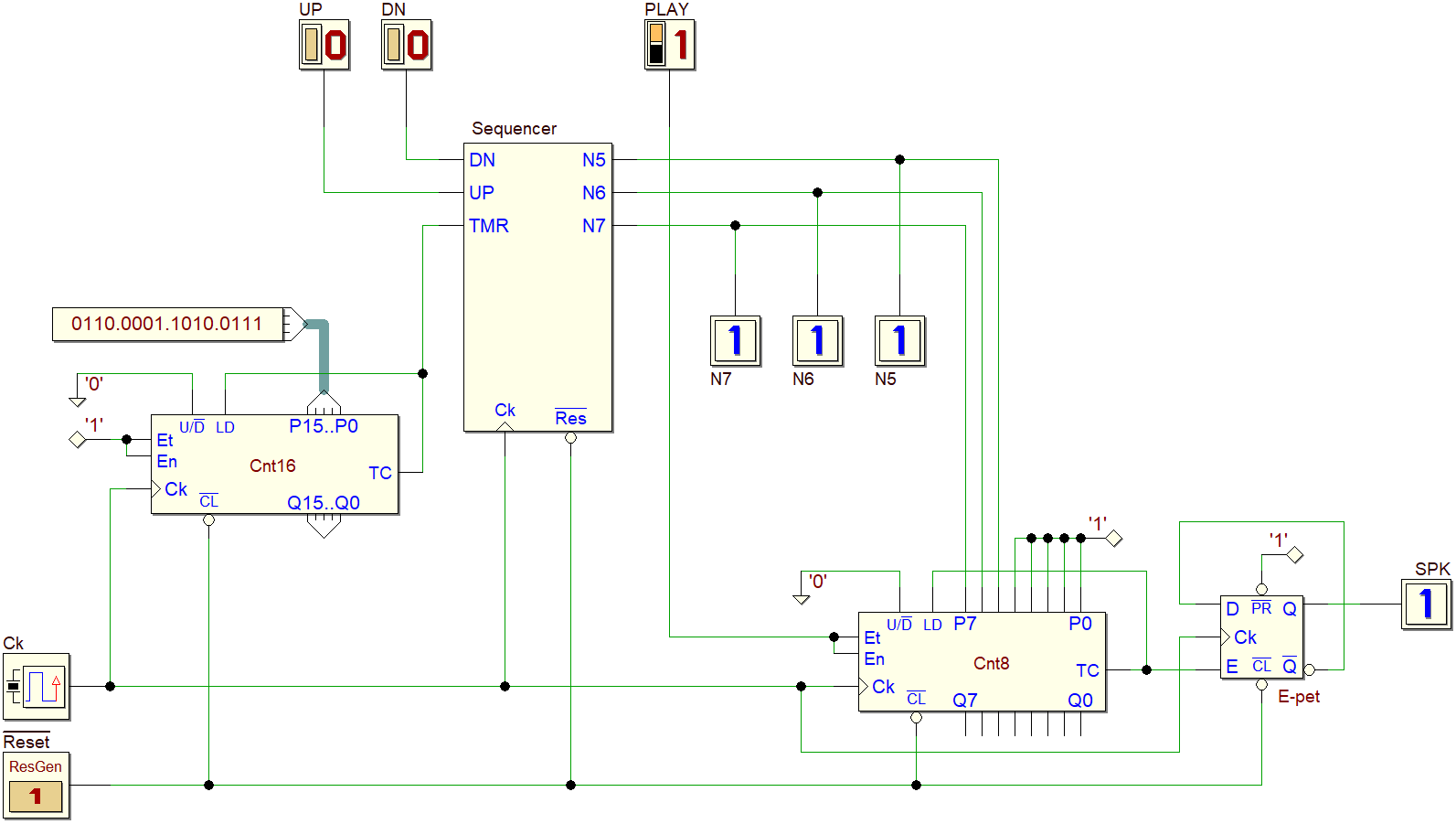

Schema circuitale:

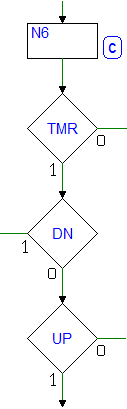

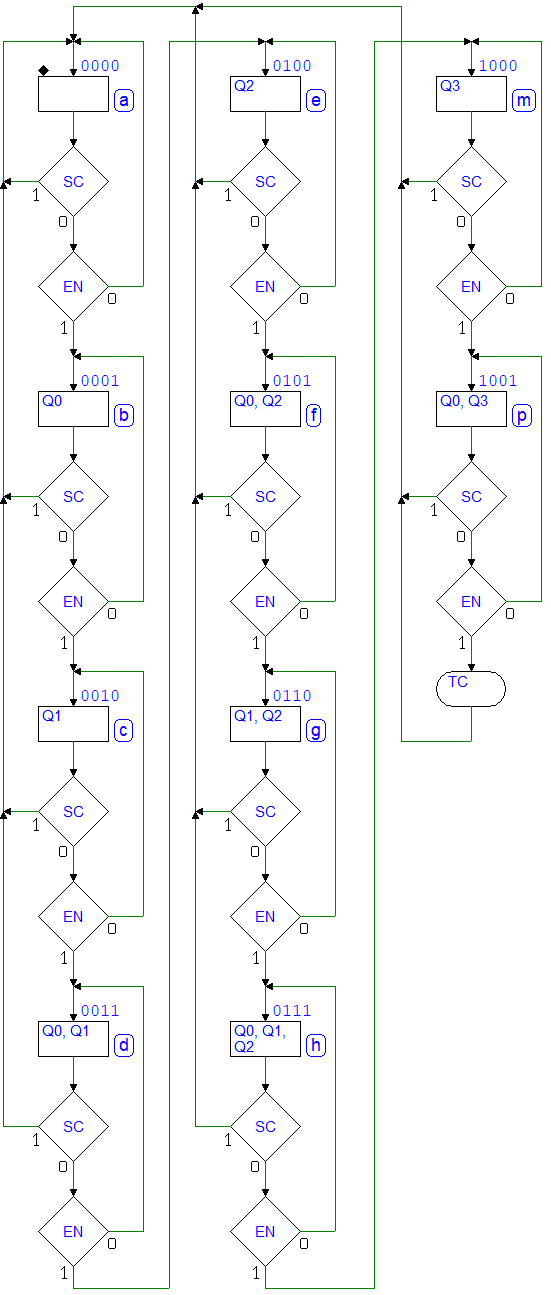

Diagramma ASM del sequenziatore:

9.4.3 Contatore di eventi

Diagramma ASM della decade:

Diagramma ASM del controllore:

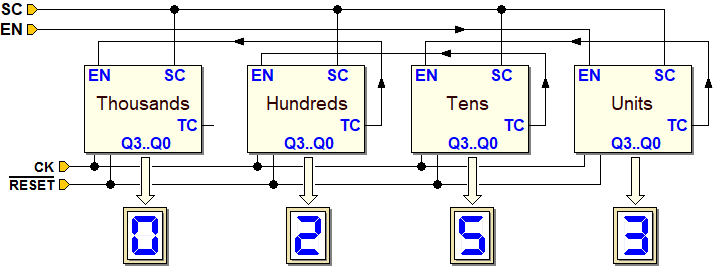

Schema circuitale CBE del contatore:

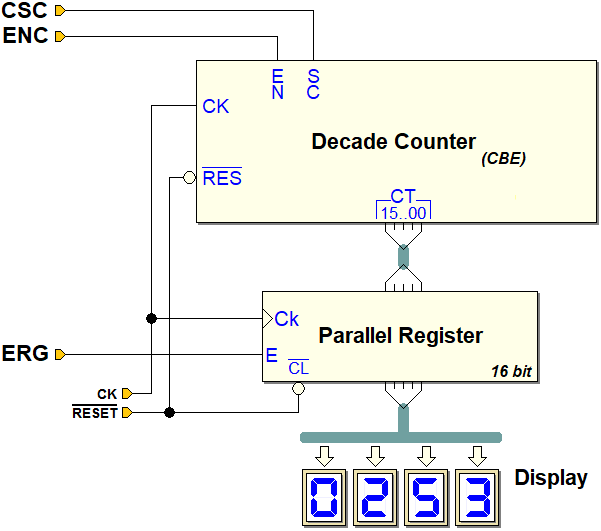

Schema circuitale complessivo:

9.4.4 Frequenzimetro

Schema circuitale CBE del contatore:

Si rimanda alla soluzione del contatore di eventi riportata in Sezione 9.4.3.

Diagramma ASM del rivelatore di fronti (Edge Detector):

Diagramma ASM del controllore del sistema (Time Base)

Schema circuitale CBE del timer:

Schema circuitale CBE del generatore di segnale:

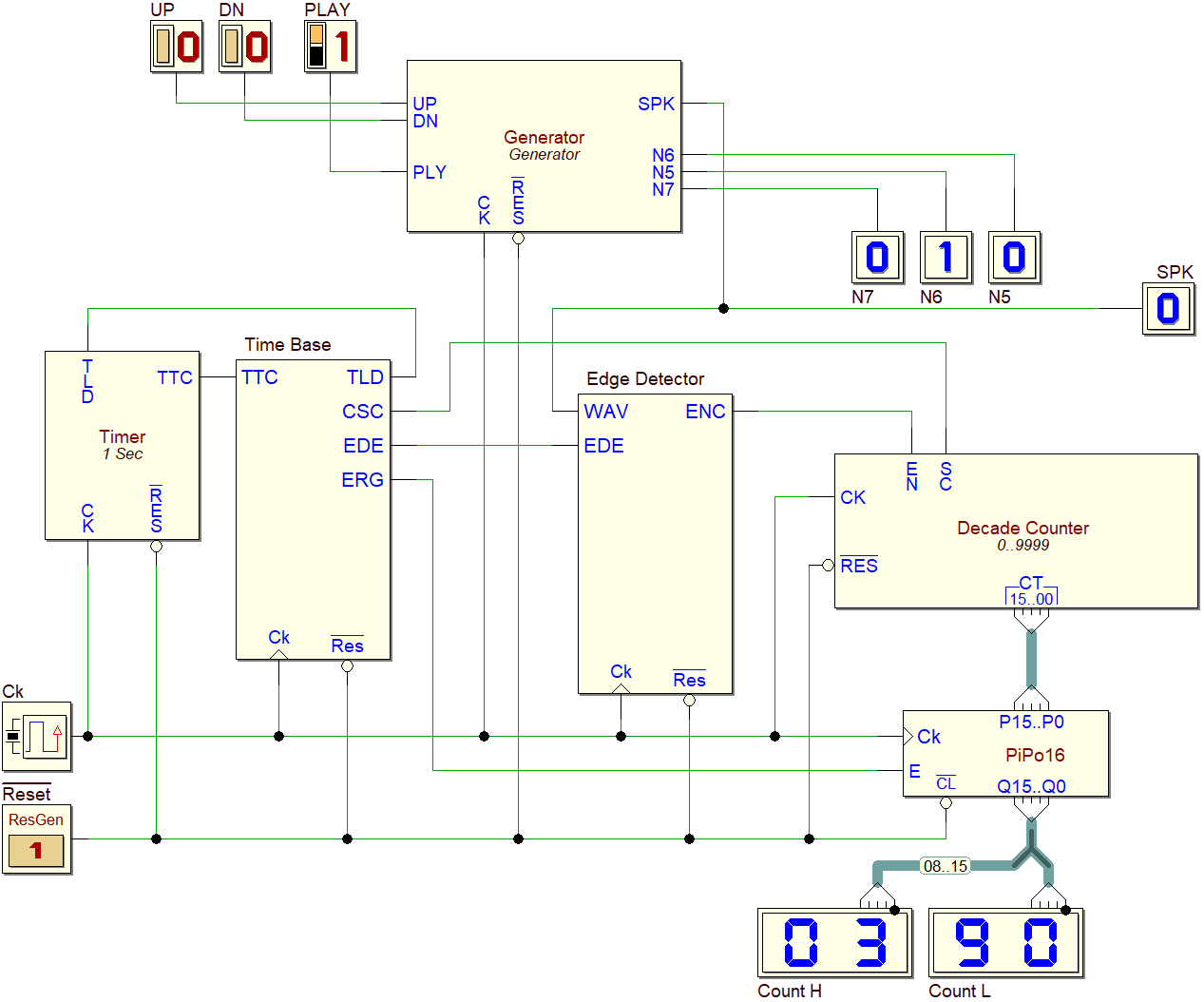

Schema circuitale complessivo del frequenzimetro

9.4.5 Sistema di comunicazione seriale sincrona (8 bit)

Diagramma ASM del controllore del trasmettitore:

Diagramma ASM del controllore del ricevitore:

Schematic (configurated for FPGA)

9.4.6 Cronometro digitale

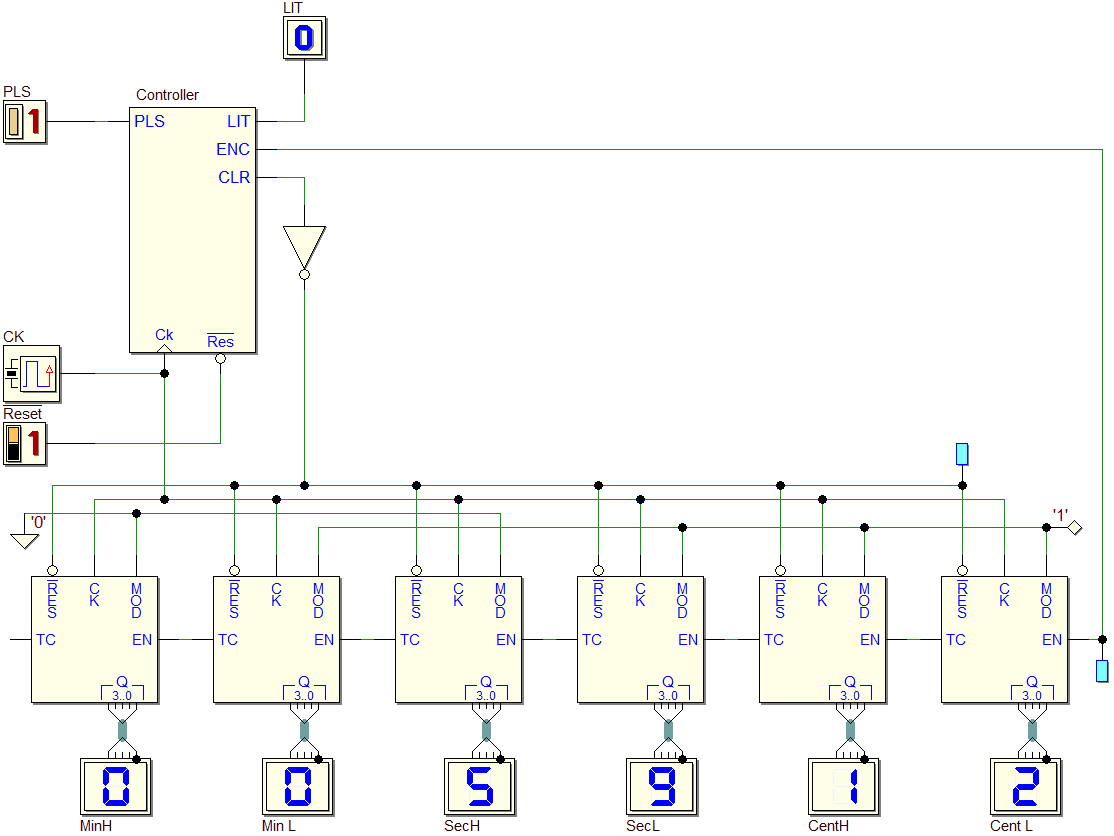

Schema complessivo ("approccio circuitale, configurato per la scheda FPGA "DE0-CV"):

Lo stesso circuito, ma senza configurazione per la scheda FPGA.

Diagramma ASM del controllore:

Modulo contatore CBE (approccio intuitivo/circuitale):

Modulo contatore CBE (approccio algoritmico/comportamentale):

Schema complessivo (approccio algoritmico, versione con CBE, configurato per la scheda FPGA "DE0-CV"). Si noti che il controller è invariato rispetto alla soluzione precedente.

Lo stesso circuito, ma senza configurazione per la scheda FPGA.

Diagramma ASM del modulo contatore CBE:

9. Errata Corrige (Chapter 9)

Pag. 504

Elenco dei file generati, al centro pagina. Si legga:

Pag. 522

Ultimo capoverso e listato del codice, in basso. Si legga: