Un sistema basato sul microprocessore DMC8

2.1 Il microprocessore DMC8

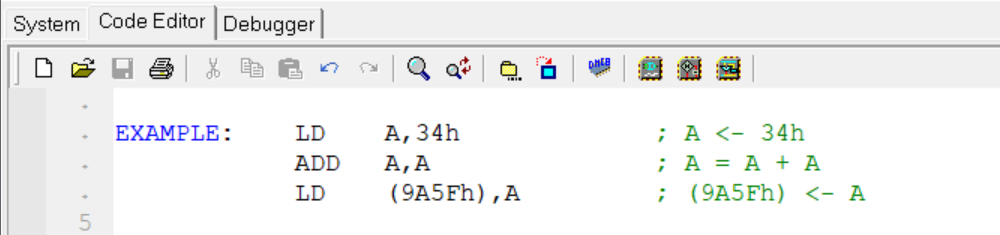

2.1.9 Un primo esempio di programmazione

2.3 I sottosistemi di memoria e di ingresso e uscita

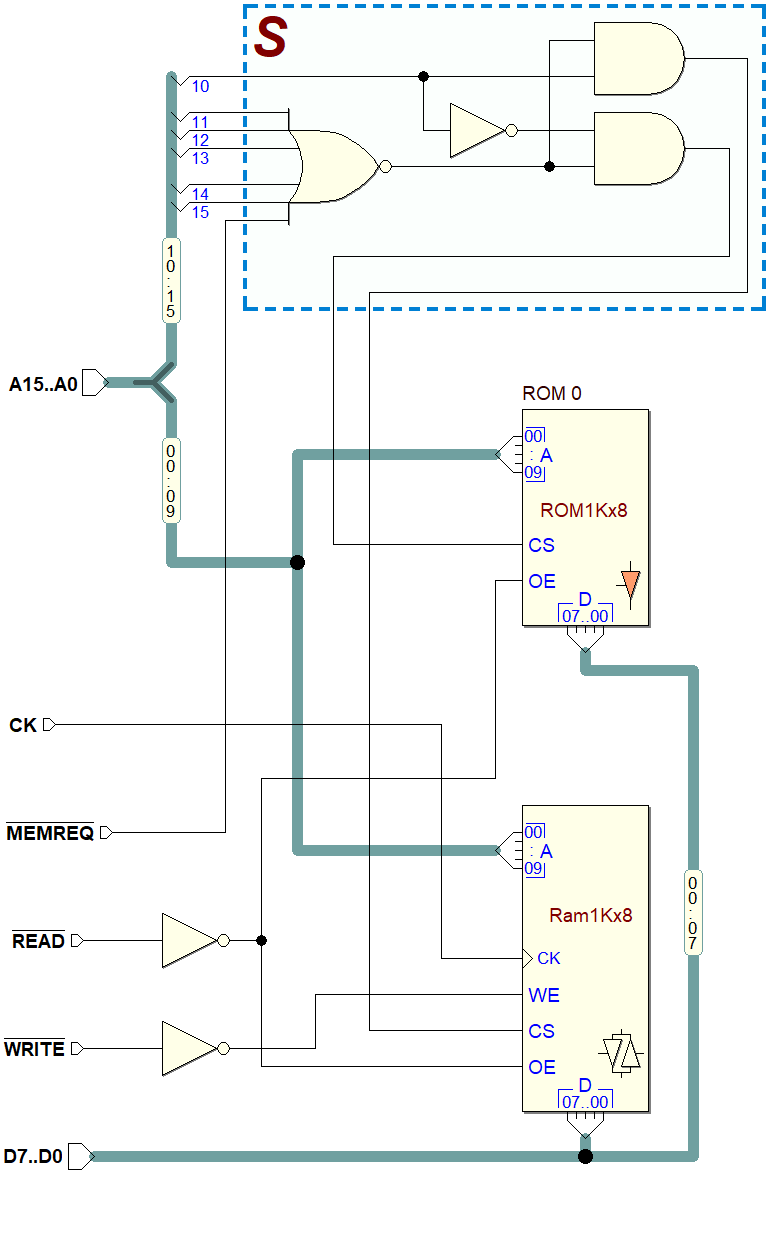

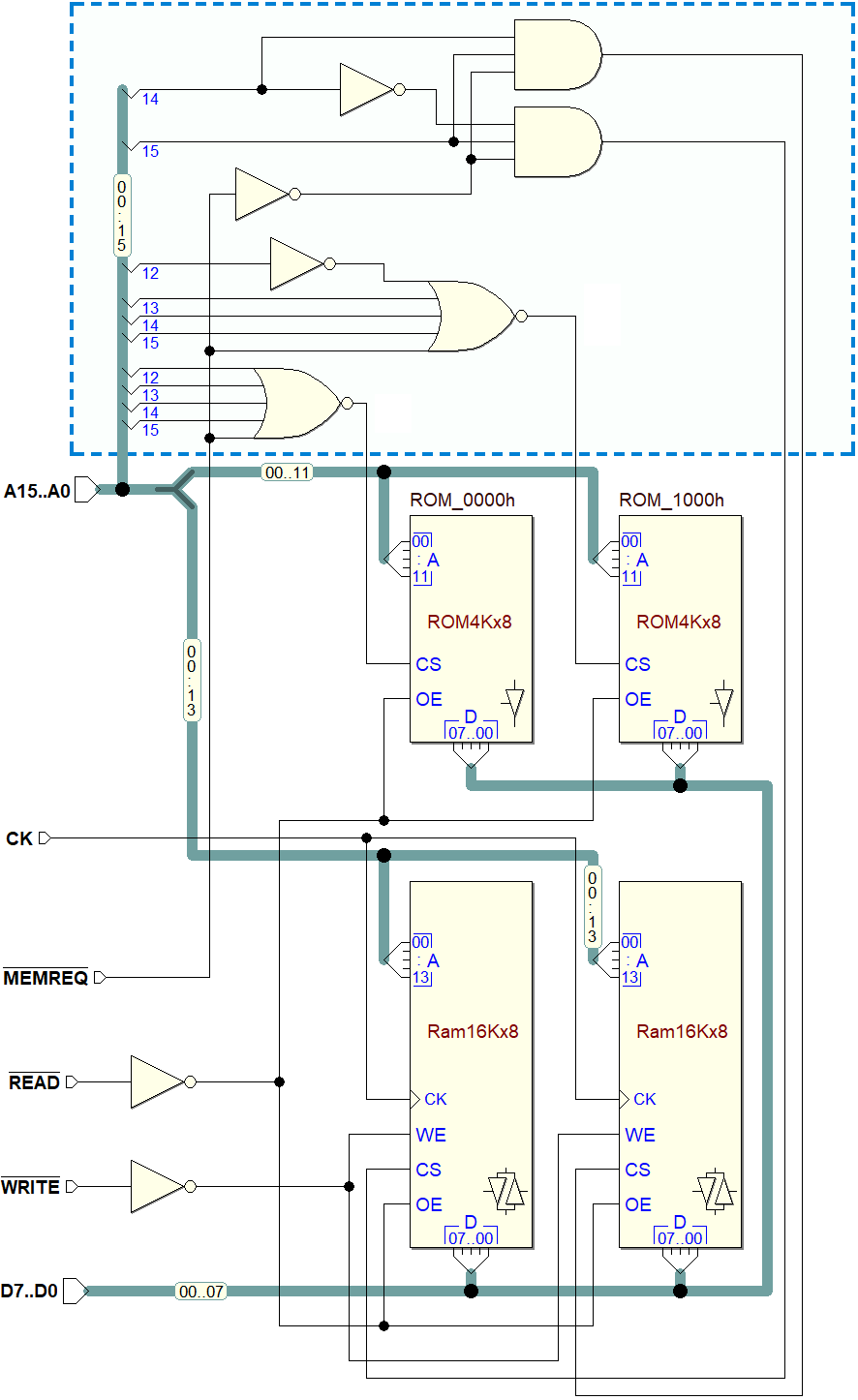

2.3.1 Il sottosistema di memoria

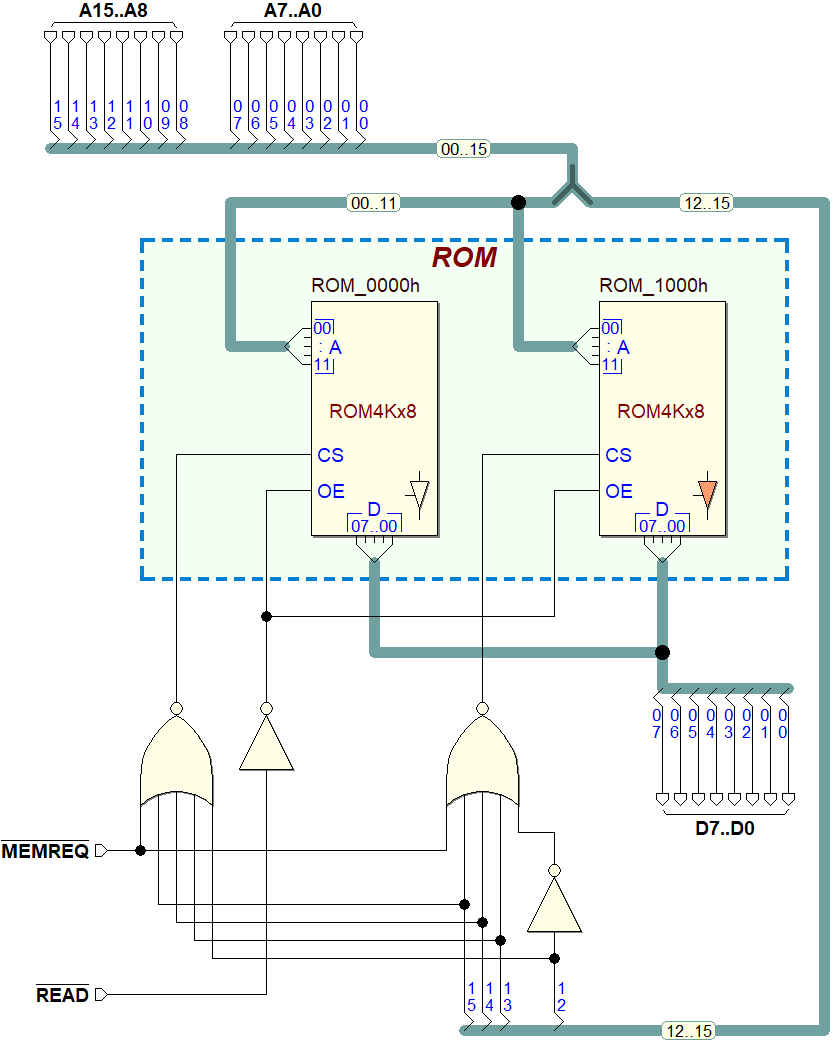

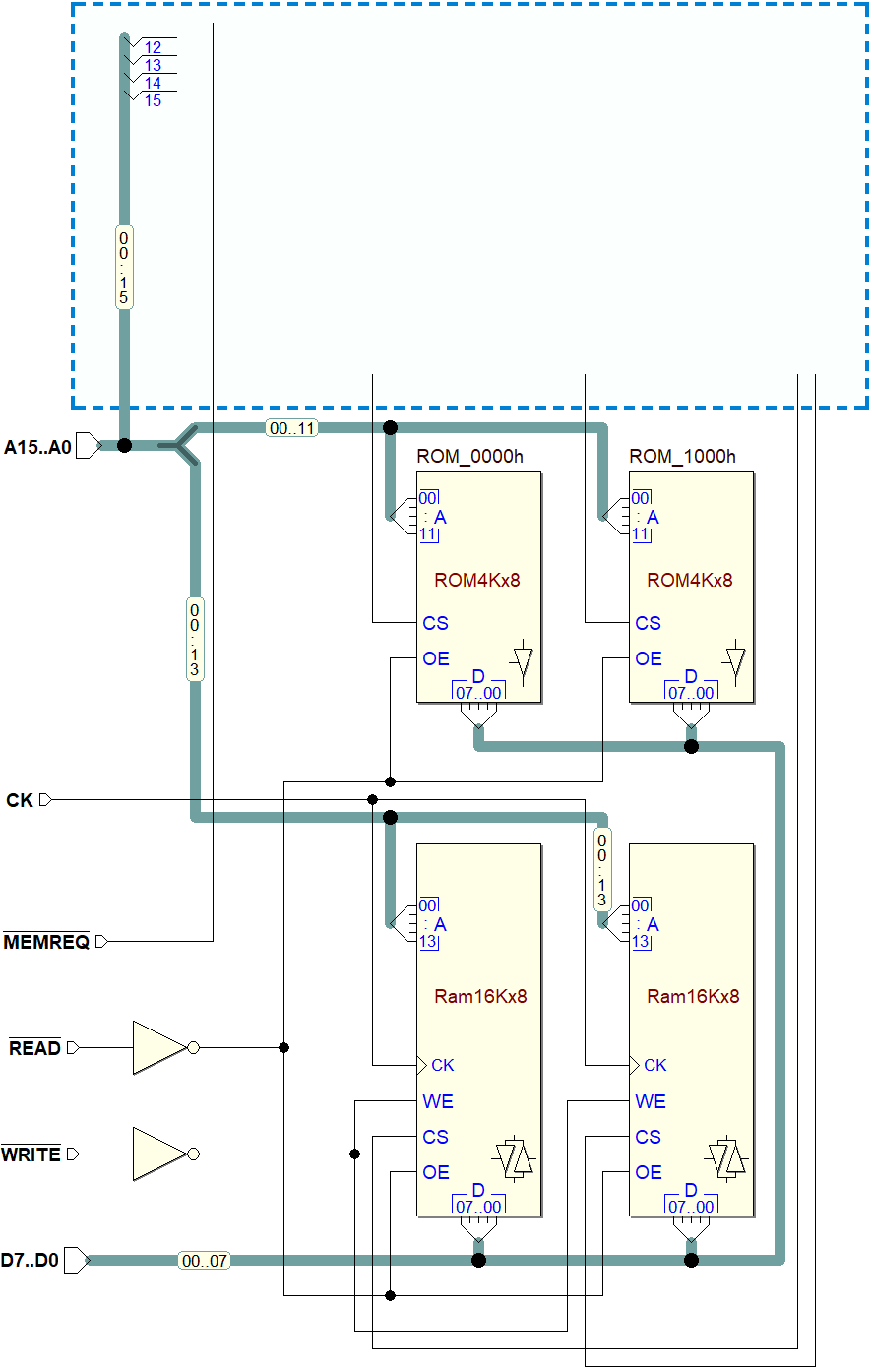

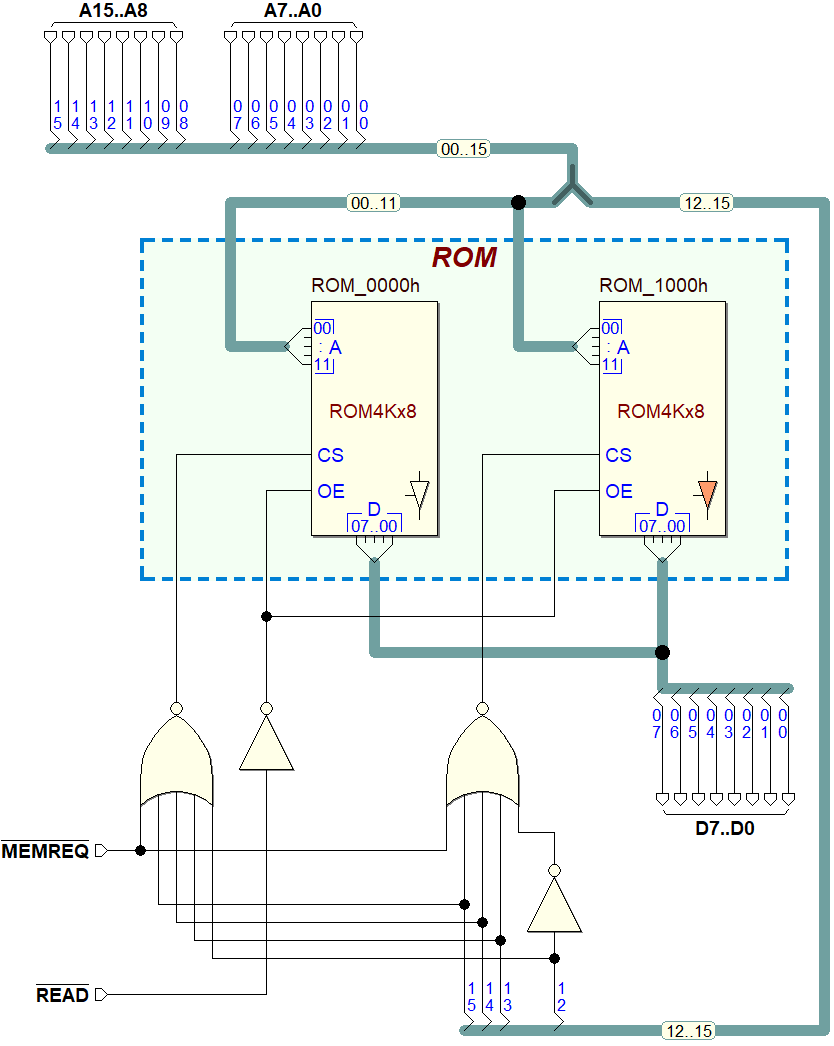

Esempio di sistema di memoria di sola lettura (ROM).

La simulazione può essere eseguita in animazione, prestando attenzione all'indirizzo fornito alle memorie, che deve essere compreso tra 0000h e 1FFFh. Attivando a zero sia !MEMREQ che !READ, si otterrà sul bus dati la lettura delle locazioni di ROM (sono state programmate, a scopo di test, solo le prime 4 locazioni di ciascun dispositivo).

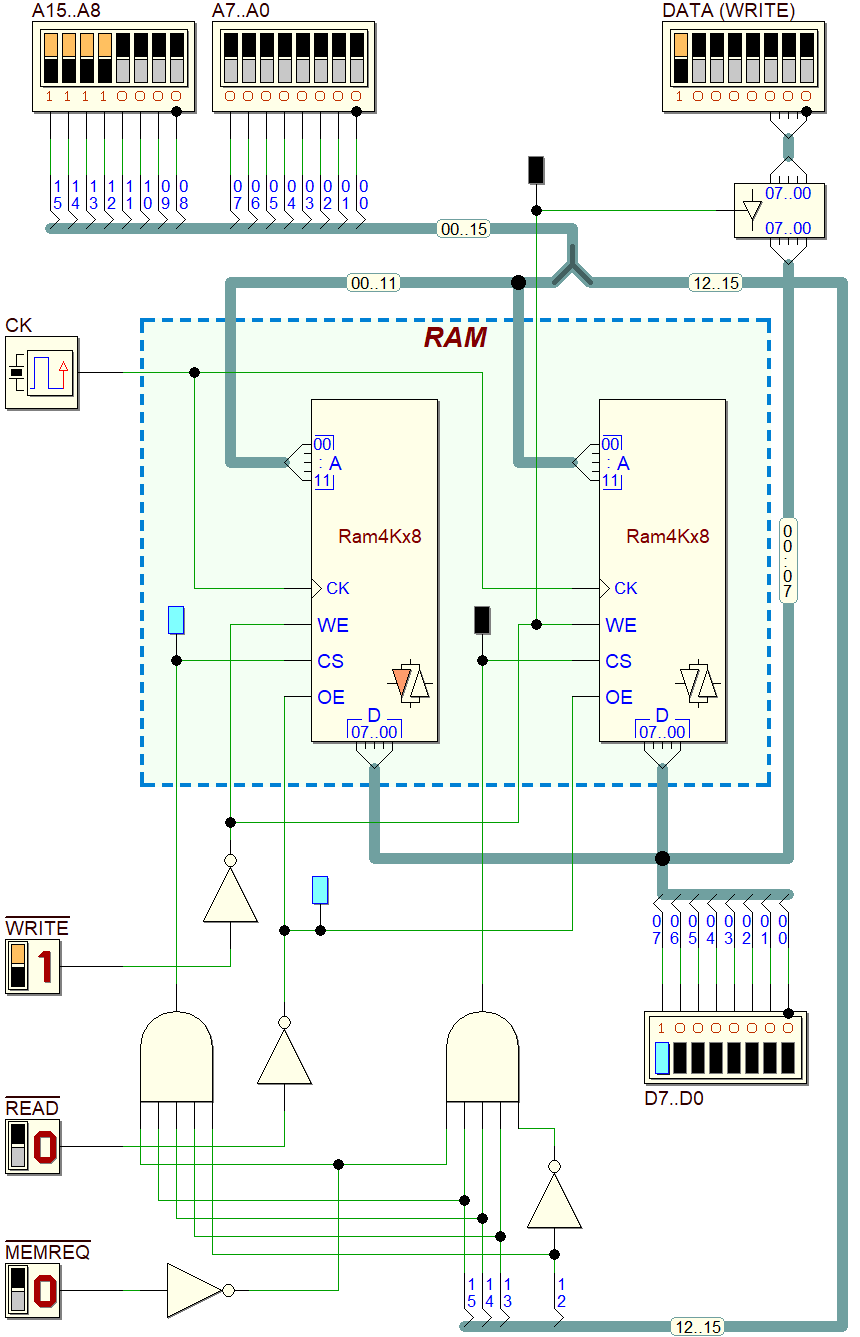

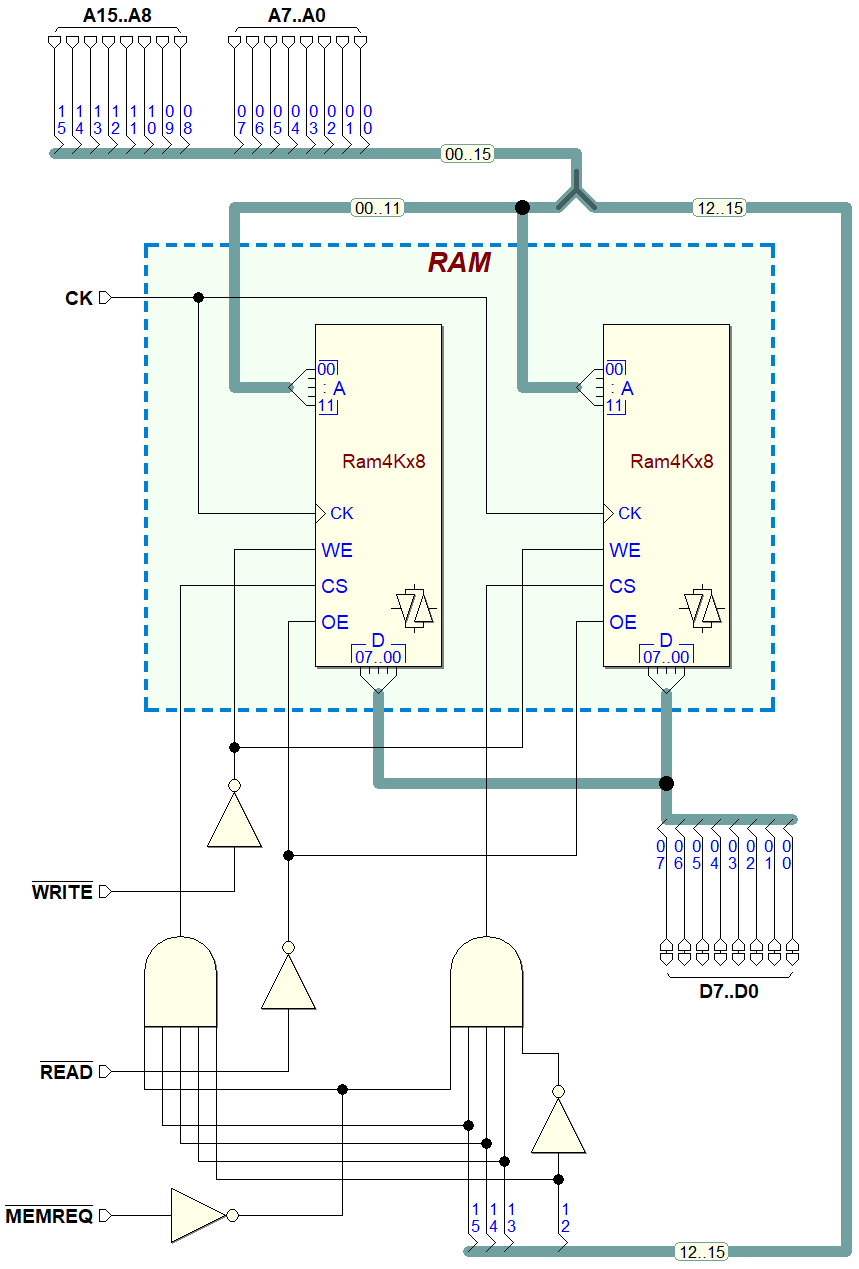

Esempio di sistema di memoria di scrittura/lettura (RAM)

Questa è la figura riportata nel libro (si veda la nota sotto alla figura):

Per simulare la rete, tuttavia, è necessario aggiungervi un buffer tri-state che ci permetta di fornire sul bus il dato da scrivere. Facendo click sulla figura seguente, si aprirà nel Deeds-DcS la rete predisposta per la simulazione.

La simulazione può essere eseguita in animazione, prestando attenzione all'indirizzo fornito alle memorie, che deve essere compreso tra E000h e FFFFh.

Prima di avere scritto qualcosa di significativo nella RAM, le locazioni risulteranno contenere valori casuali e quindi, per il simulatore, indeterminati. Infatti, attivando sia !MEMREQ che !READ (portandoli a zero), sul bus dati si otterrano dei valori sconosciuti, qualunque indirizzo interno alla RAM si fornisca.

Per scrivere un dato:

- Si imposta il valore del dato all'ingresso del buffer tri-state collegato agli switch denominati WRITE DATA;

- Si definisce l'indirizzo della locazione che si vuole scrivere;

- Si attiva (a zero) la richiesta della memoria !MEMREQ;

- Si attiva (a zero) il comando di scrittura !WRITE e si attende il successivo fronte di salita del clock;

- Si disattivano !MEMREQ e !WRITE.

Come verifica della avvenuta scrittura, si tratta ora di:

- Mantenere uguale a prima l'indirizzo della locazione che si vuole leggere;

- Attivare nuovamente la richiesta della memoria !MEMREQ;

- Portare a zero il comando di lettura !READ, attendendo il successivo fronte di salita del clock;

- Il dato comparirà sul bus, pronto per essere utilizzato;

- Per concludere la lettura, occorrerà poi disattivare !MEMREQ e !READ.

2.3.2 Il sottosistema di ingresso e uscita

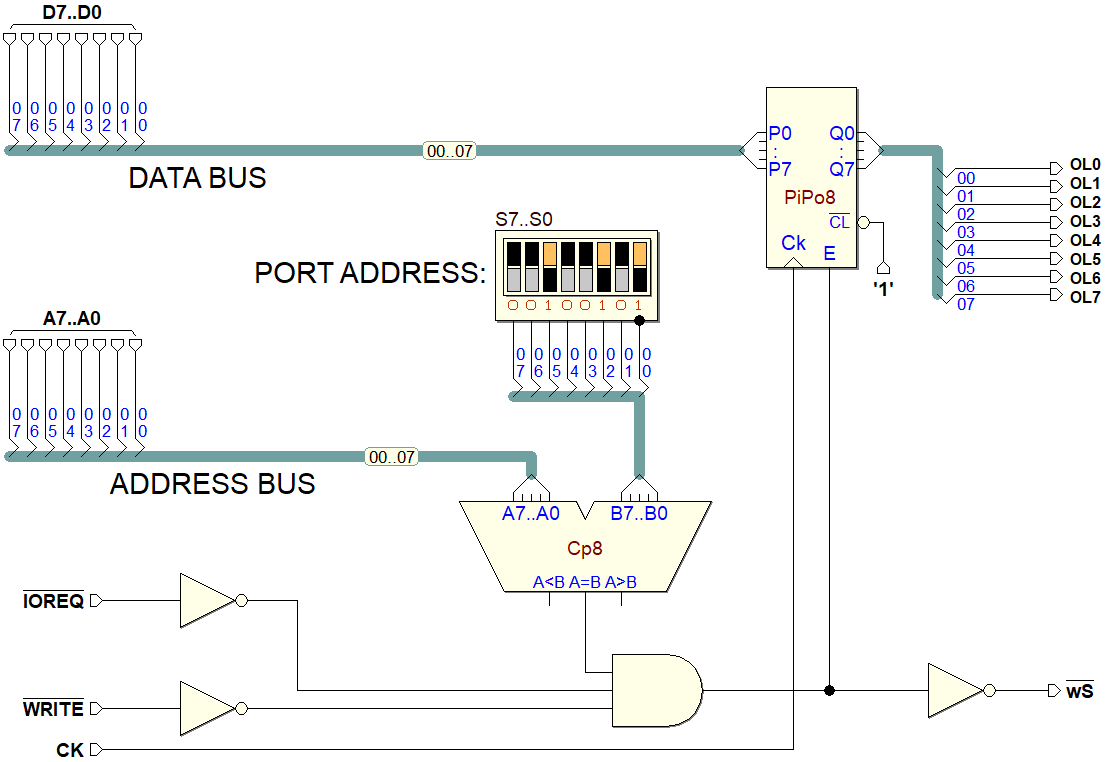

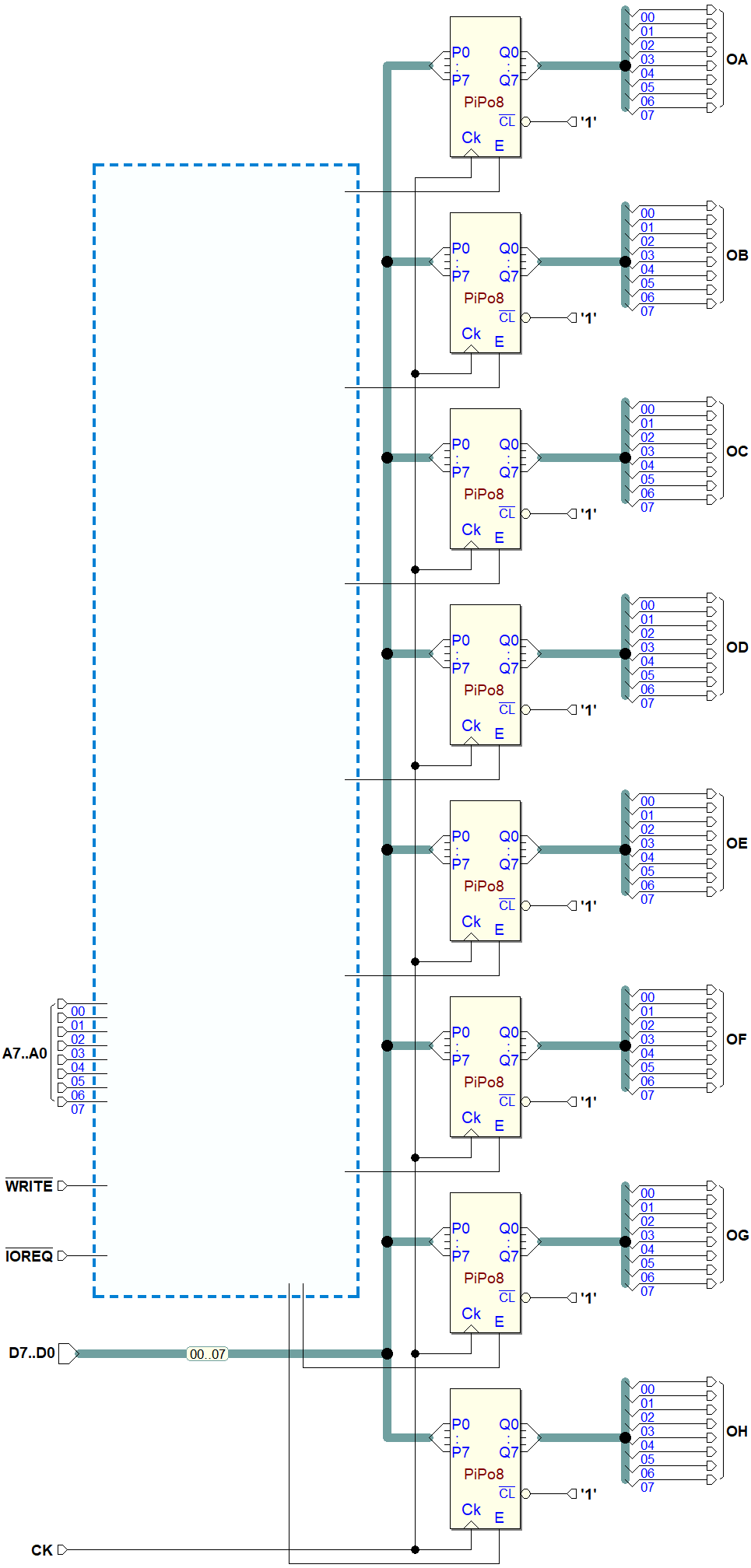

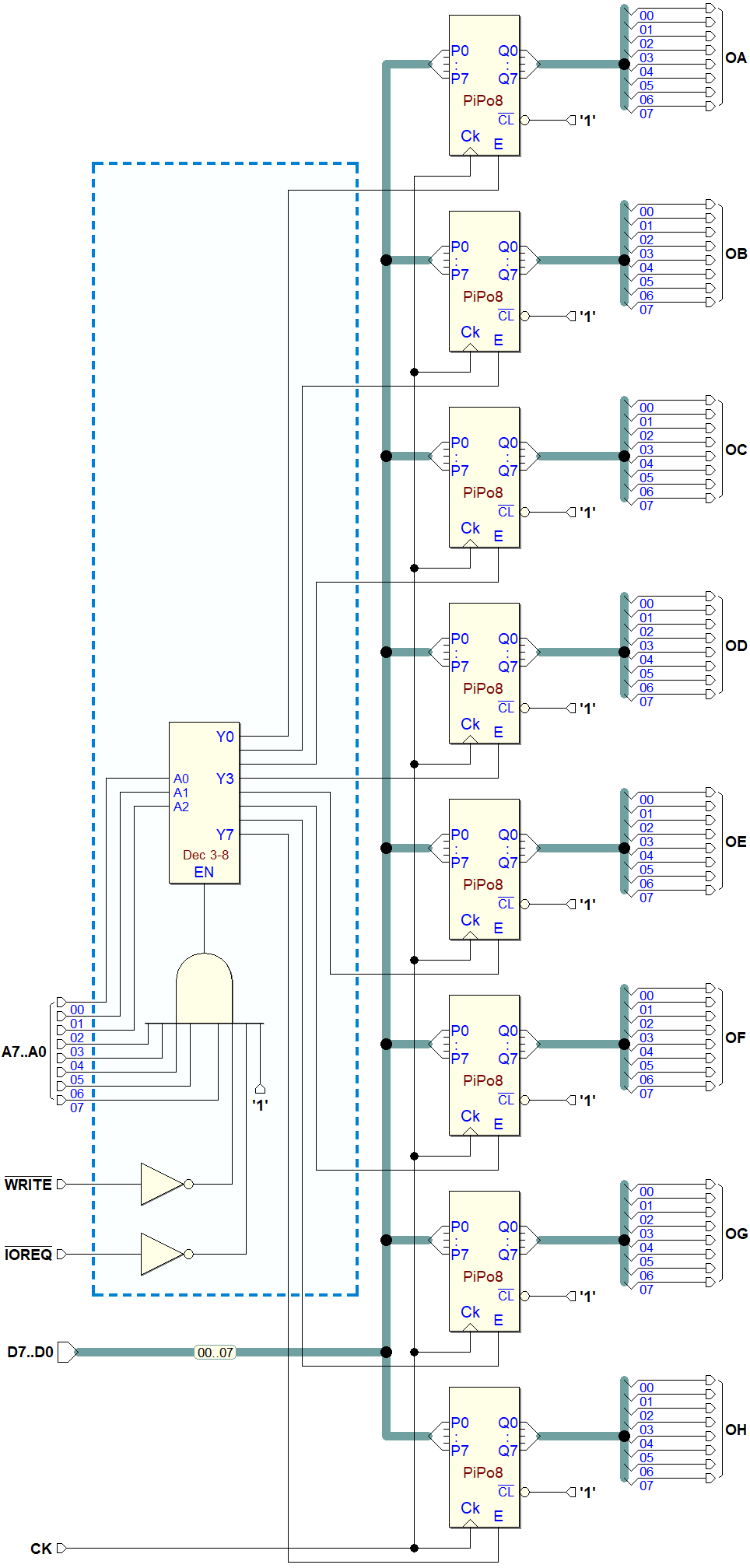

2.3.2.1 I porti paralleli di uscita

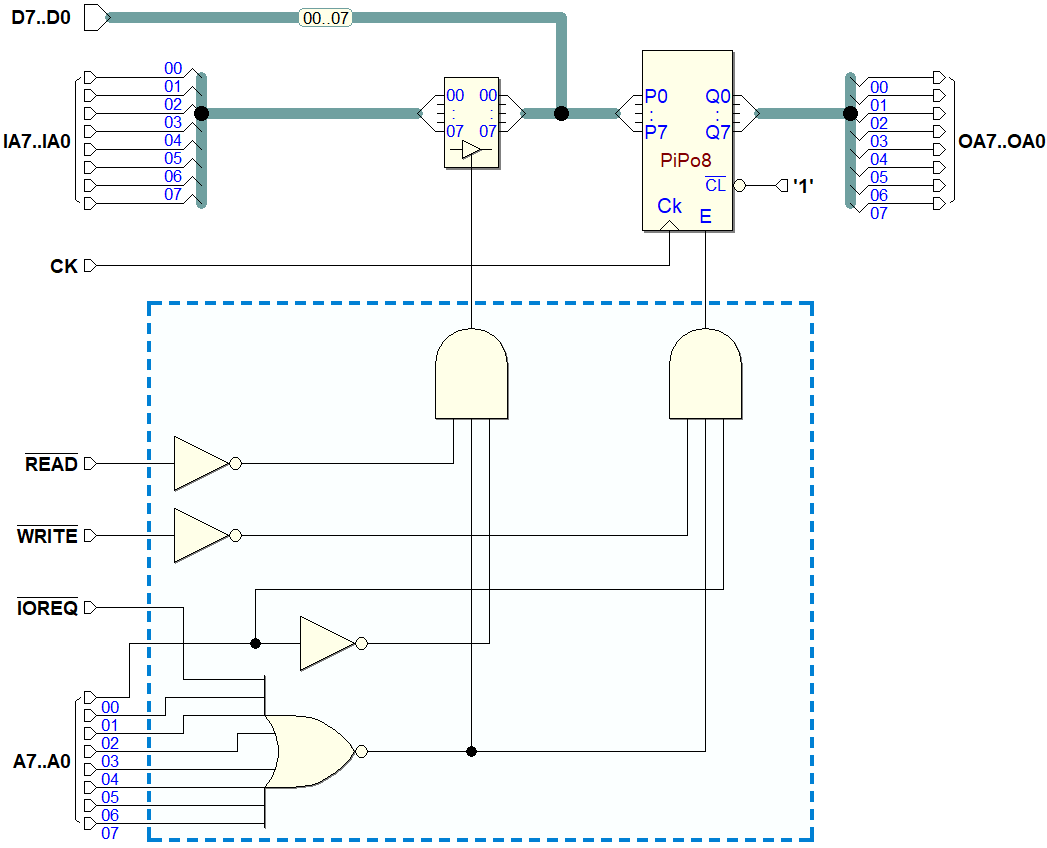

Esempio di porto parallelo di uscita, con indirizzo definibile mediante interruttori. La simulazione può essere eseguita in animazione.

Per scrivere un dato nel porto di uscita:

- Si fornisce l'indirizzo del porto (25h in questo esempio);

- Si imposta il valore presente sul bus dei dati;

- Si attiva (a zero) la richiesta di Ingresso/Uscita !IOREQ;

- Si attiva (a zero) il comando di scrittura !WRITE e si attende il successivo fronte di salita del clock;

- Si disattivano !IOREQ e !WRITE.

Il dato rimarrà memorizzato sul registro fino ad una nuova scrittura. Si faccia attenzione al fatto che il porto non può essere riletto (non sono presenti i circuiti per la rilettura).

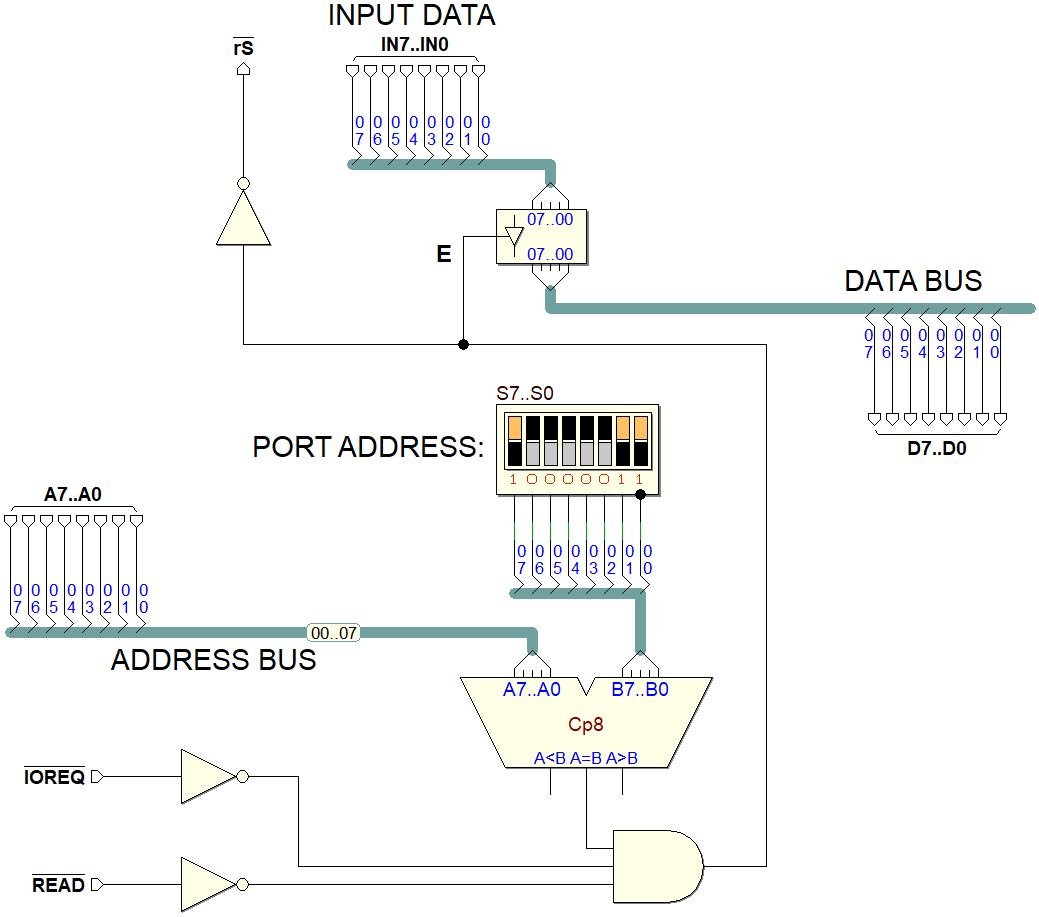

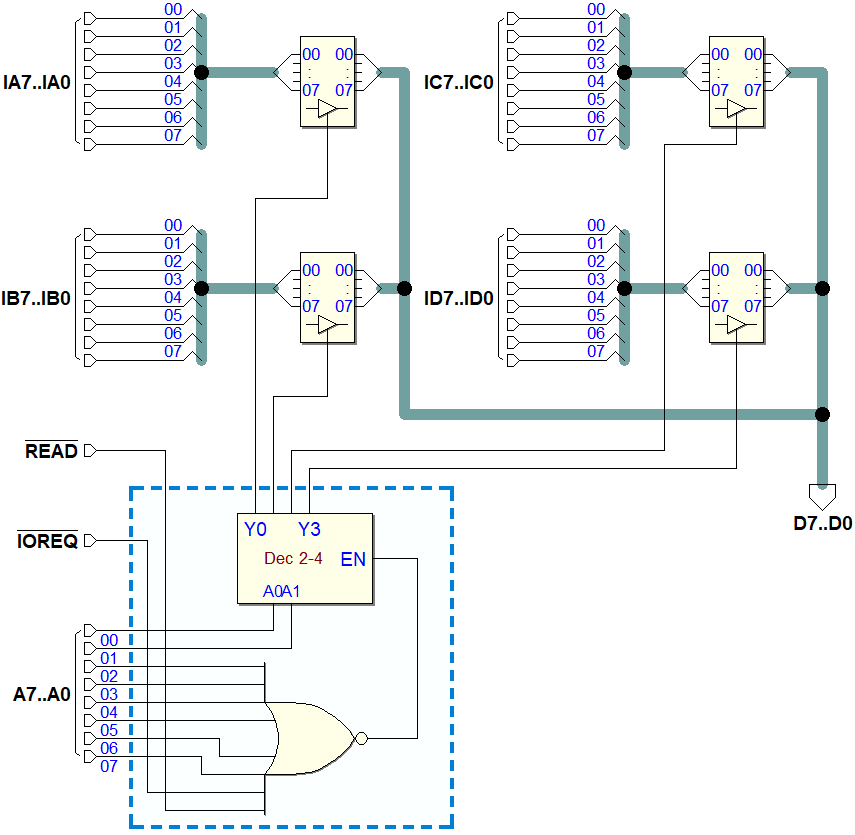

2.3.2.2 I porti paralleli di ingresso

Esempio di porto parallelo di ingresso, con indirizzo definibile mediante interruttori. La simulazione può essere eseguita in animazione. Si suppone che il 'mondo esterno' ci fornisca il dato da acquisire, tramite le linee INPUT DATA.

- Tramite il bus degli indirizzi generiamo l'indirizzo del porto da leggere (impostato sugli interruttori a 83h, in questo esempio);

- Si attiva (a zero) la richiesta di Ingresso/Uscita !IOREQ;

- Si attiva (a zero) il comando di lettura !READ, per cui il buffer tri-state farà comparire il dato sul bus, pronto per essere letto dal processore;

- Si disattivano !IOREQ e !READ, disimpegnando il bus.

2.5 Esercizi

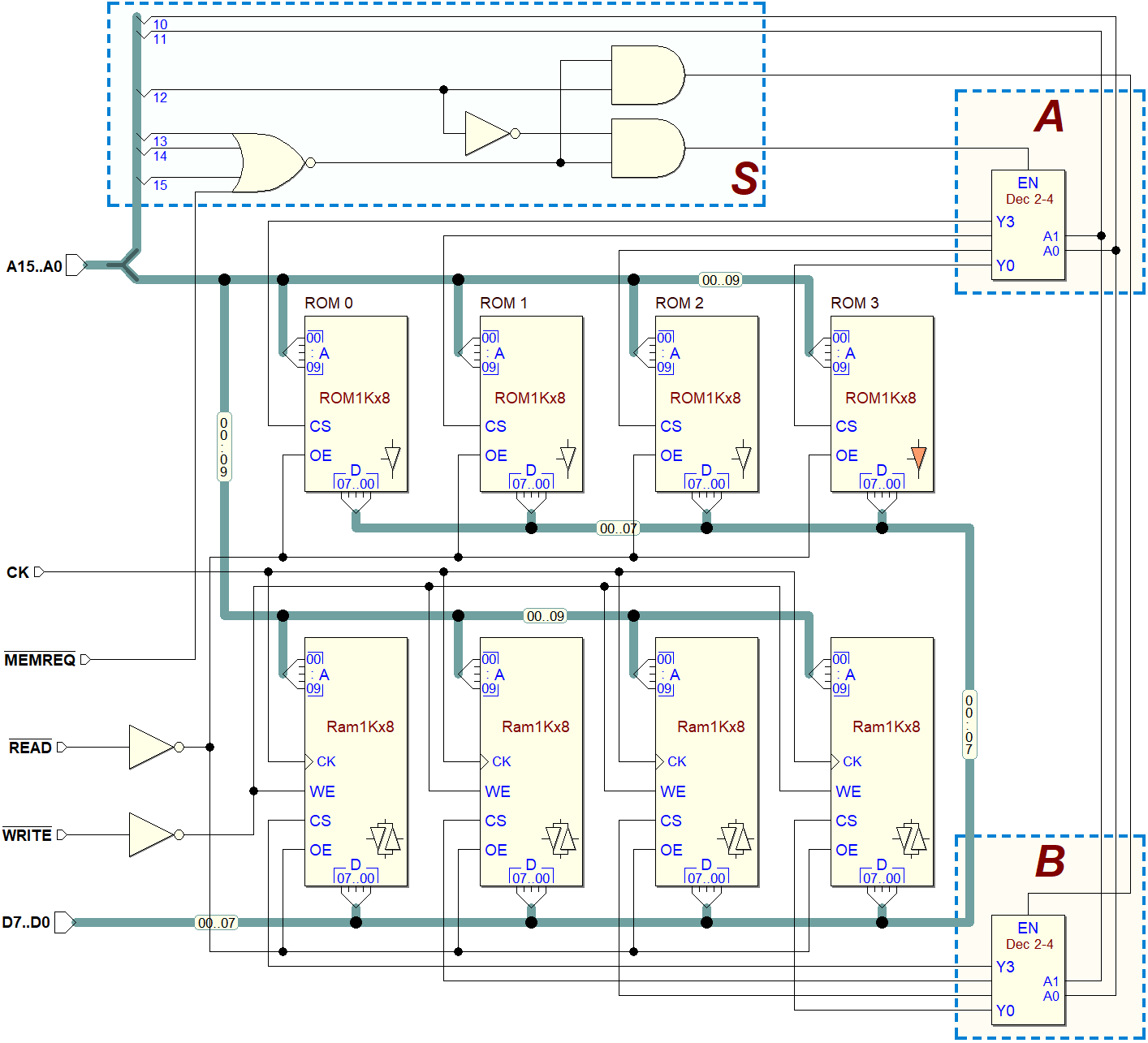

2.5.1 Sistemi di memoria

Facendo click sulla figure proposte, si apriranno nel Deeds-DcS le reti predisposte per la simulazione. Un buffer tri-state è stato aggiunto alle reti, per consentire di fornire sul bus il dato da scrivere.

Esercizio 2 (schema da analizzare):

Esercizio 3 (schema da analizzare):

Esercizio 4 (schema da completare):

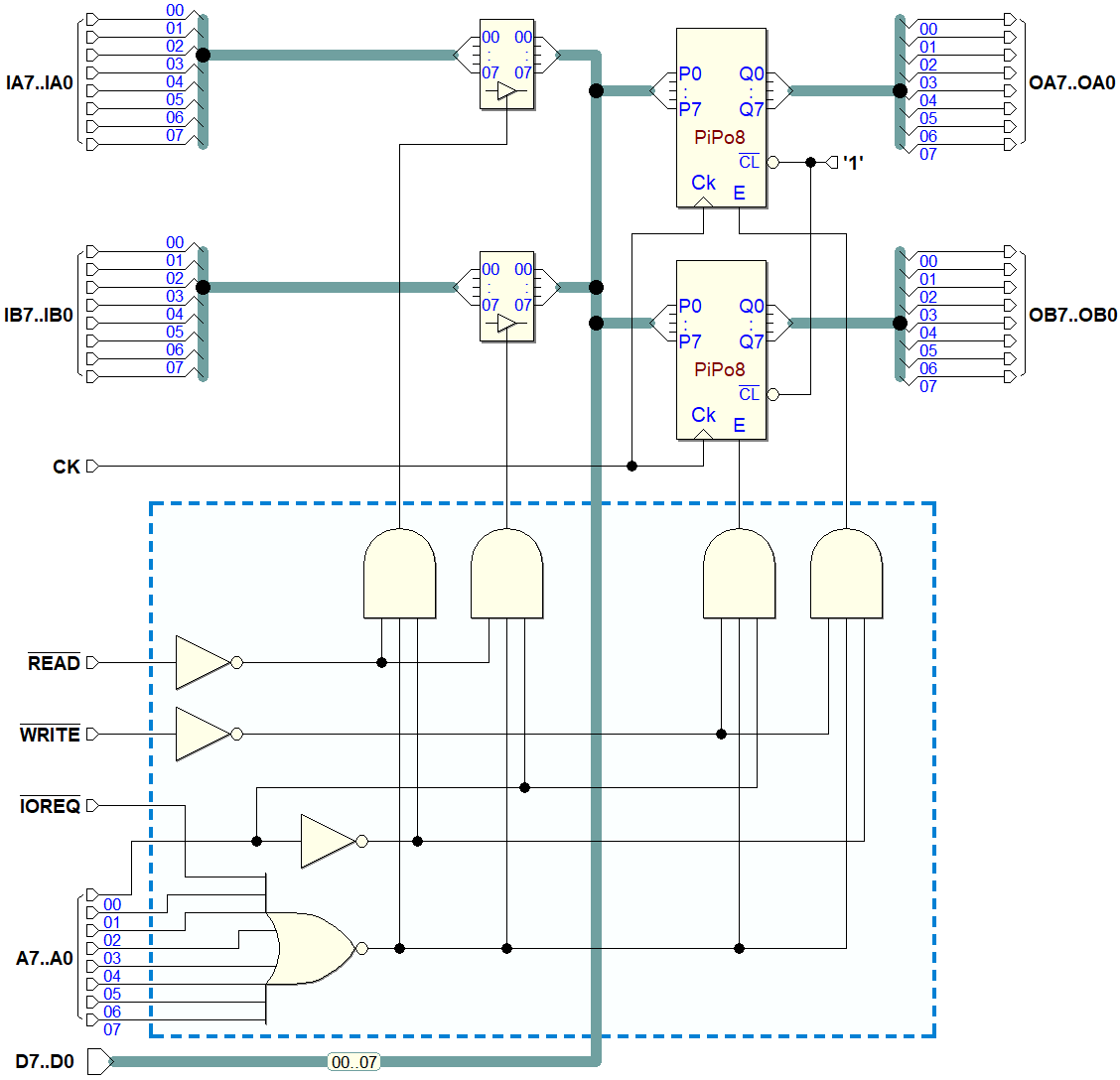

2.5.2 Porti paralleli di ingresso e uscita

Facendo click sulla figure proposte, si apriranno nel Deeds-DcS le reti predisposte per la simulazione. Un buffer tri-state è stato aggiunto alle reti, quando necessario, per consentire di fornire sul bus il dato da copiare sul porto.

Esercizio 1a (schema da analizzare):

Esercizio 1b (schema da analizzare):

Esercizio 1c (schema da analizzare):

Esercizio 2 (schema da completare):

2.6 Soluzioni

2.6.1 Sistemi di memoria

Soluzione esercizio 4:

Facendo click sulla figura, si aprirà nel Deeds-DcS la rete, predisposta per la simulazione. Un buffer tri-state è stato aggiunto, per consentire di fornire sul bus il dato da scrivere nella RAM.

2.6.2 Porti paralleli di ingresso e uscita

Soluzione esercizio 2:

2. Errata Corrige (Cap. 2)

Pag. 131

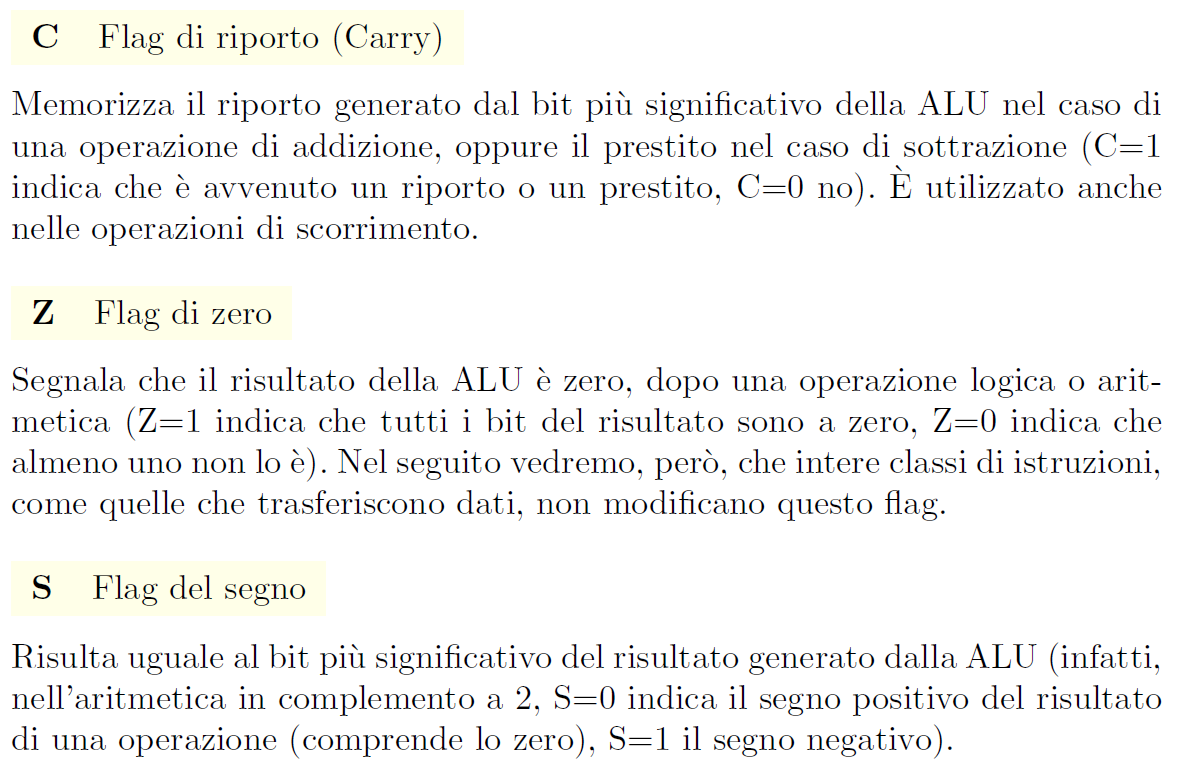

Descrizione dei flag C, Z e S. Si legga:

Pag. 152

Nella figura, l'etichetta della memoria ROM sulla destra dovrebbe riportare "ROM_1000h". Qui la figura corretta:

Pag. 171

Sesto capoverso, al centro pagina. Si legga:

Pag. 188

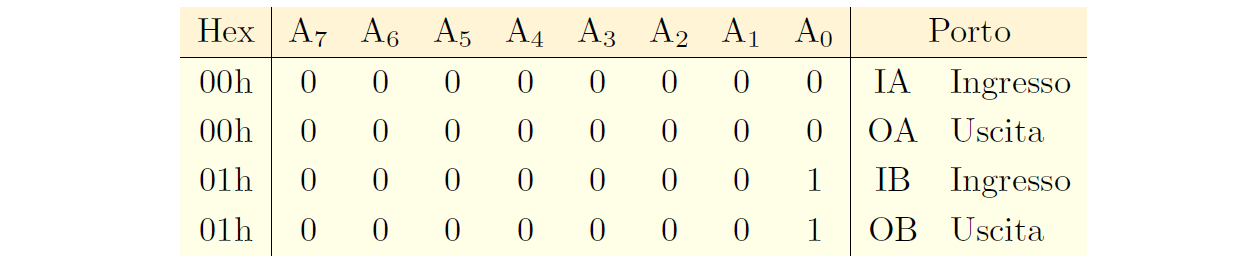

Soluzione esercizio 1.C, mappa dei porti al centro pagina. Si legga: