|

|

||||||||||

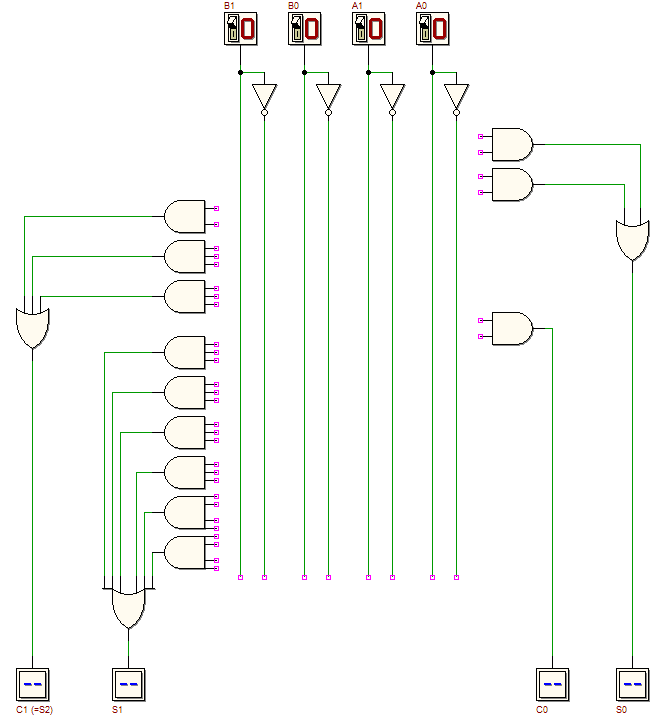

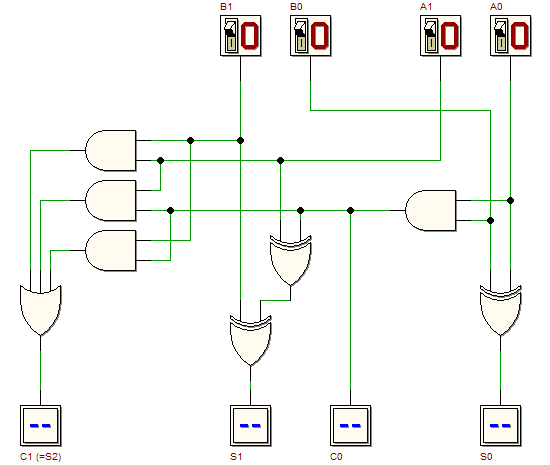

| Si consideri la rete in figura (un click su di essa aprirà lo schema nel d-DcS). Questo circuito combinatorio è un sommatore a due bit, composto da un semi-sommatore (l' AND e l' EXOR sulla destra) e da un sommatore completo (le sei porte logiche sulla sinistra). Si osservi che questo schema non descrive una rete a due livelli. Utilizzando la simulazione funzionale Si chiede di progettare una rete AND-OR a due livelli che abbia la stessa funzionalità, realizzando un sommatore veloce a due bit. Lo definiamo veloce perchè, grazie alla realizzazione a due livelli, il tempo di propagazione tra ingresso e uscita risulterà ridotto rispetto all'esempio dato (questo caratteristica sarebbe maggiormente in evidenza considerando un sommatore tra numeri rappresentati con molti bit). Si compili una mappa di Karnaugh per ciascuna uscita e si scrivano le espressioni delle sintesi minime. Si disegni lo schema della rete che ne risulta: un click sulla figura seguente aprirà nel d-DcS lo schema da completare. Verificare il corretto funzionamento della rete dapprima con una simulazione funzionale | |||||||||||

, si considerino tutte le possibili combinazioni dei valori degli ingressi e si compili la tavola di verità della rete. Si verifichi il corretto funzionamento della rete anche con una simulazione temporale

, si considerino tutte le possibili combinazioni dei valori degli ingressi e si compili la tavola di verità della rete. Si verifichi il corretto funzionamento della rete anche con una simulazione temporale  che ne dimostri il funzionamento. Si suggerisce di utilizzare la sequenza di test disponibile nella finestra del diagramma temporale.

che ne dimostri il funzionamento. Si suggerisce di utilizzare la sequenza di test disponibile nella finestra del diagramma temporale.