|

|

||||||||||

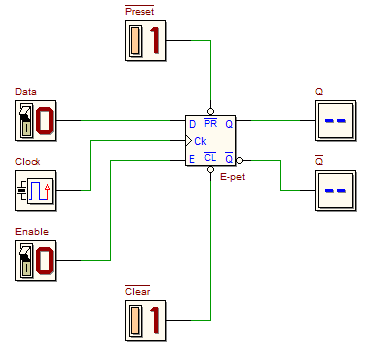

| Verify the behavior of the following simple sequential network, based on a E-PET Flip-Flop component. You can open it in the d-DcS, with a click on the figure: Verify, using the timing simulation Remember that the !Preset and !Clear inputs are normally used to initialise the component (at the beginning), but sometimes they can be used also to Set or Reset the device, asynchronously, during the normal operations of the network. | |||||||||||

,

the behavior of the flip-flop. Pay attention to put in evidence, in the timing diagram, the meaningful combinations of input values (a suitable test sequence is available in the Timing Diagram window, including !Preset and !Clear activation).

,

the behavior of the flip-flop. Pay attention to put in evidence, in the timing diagram, the meaningful combinations of input values (a suitable test sequence is available in the Timing Diagram window, including !Preset and !Clear activation).