|

|

||||||||||

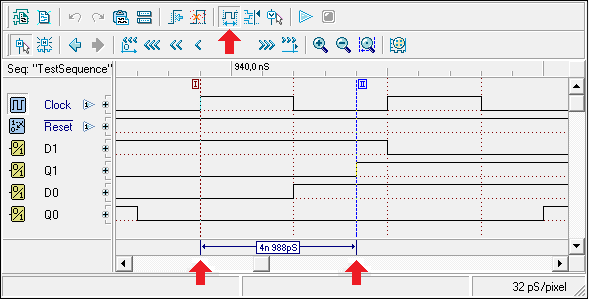

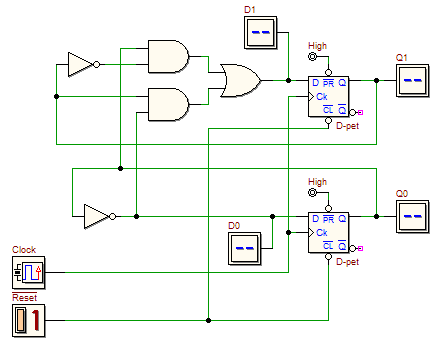

| La rete sequenziale rappresentata in figura è un contatore in avanti modulo 4, realizzato con flip-flop D-PET. Si apra lo schema nel d-DcS con un click sulla figura: Q1 e Q0 sono le uscite del contatore. Mediante una simulazione temporale Oltre questa frequenza, il circuito non svolge più la sua corretta funzione perchè la rete combinatoria non dispone più del tempo sufficiente per generare il valore degli ingressi dei flip-flop prima del successivo fronte di salita del clock. Per facilitare la comprensione, sono stati aggiunti, nello schema, le uscite "di test" D1 e D0 delle due reti combinatorie. Si confrontino i risultati della simulazione nel caso normale (quando la frequenza è minore del massimo valore) e nel caso di errore (a frequenze più alte) . Suggerimenti 1) Per evitare confusione nel diagramma temporale,

si attivi il segnale di !Reset (a livello basso) almeno per 20 nS.

3) La misura del tempo di ritardo è facilitata dai cursori per la misura del tempo (time cursors); si possono attivare con il comando

| |||||||||||

, verificare il comportamento del circuito, dapprima lasciando impostato il clock alla frequenza assegnata nello schema (5 MHz, corrispondente a 200 nS di periodo). Poi, aumentando progressivamente la frequenza del clock, individuare la massima frequenza alla quale il circuito funziona ancora correttamente.

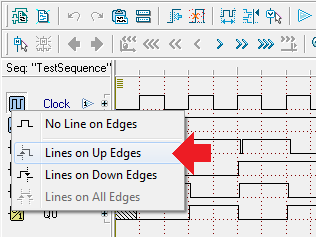

, verificare il comportamento del circuito, dapprima lasciando impostato il clock alla frequenza assegnata nello schema (5 MHz, corrispondente a 200 nS di periodo). Poi, aumentando progressivamente la frequenza del clock, individuare la massima frequenza alla quale il circuito funziona ancora correttamente. , sulla sinistra del diagramma, e scegliere il comando che posiziona le linee sul fronte di salita (Line on Up Edges), come mostrato nella figura seguente:

, sulla sinistra del diagramma, e scegliere il comando che posiziona le linee sul fronte di salita (Line on Up Edges), come mostrato nella figura seguente:

(vedi figura seguente).

(vedi figura seguente).