|

|

||||||||||

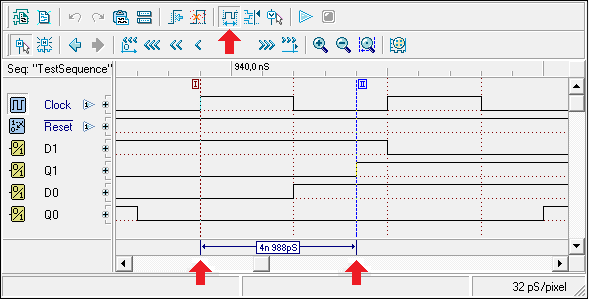

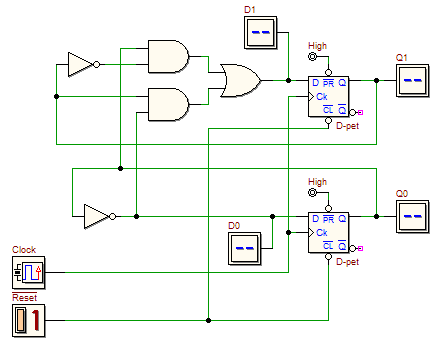

| The following circuit is a module-4 Up-Counter, synthesized with D-PET flip-flops. Click on the figure to open in the d-DcS the counter schematic: Q1 and Q0 are the counter outputs. Using the d-DcS timing simulator Beyond this clock frequency, the network fails, because the combinational network cannot provide the correct input to the flip-flops within the next clock rising-edge. The D1 and D0 outputs have been added to the schematic to facilitate the understanding of this process. You should compare the timing diagram resulting from the simulation of the normal case (where the frequency is lower than the maximum working frequency), and of the fault case (frequency higher). Suggestions 1) To avoid confusion in the timing diagram,

activate low the !Reset signal at least for

20 nS.

3) For the time delay measurement, you could activate the time cursors, using the button

| |||||||||||

, verify the circuit behavior as it is given, without changing the given clock frequency (5 MHz, corrisponding to a period of 200 nS). Then, find the (approximate) maximum Clock frequency for which the counter

is still working correctly.

, verify the circuit behavior as it is given, without changing the given clock frequency (5 MHz, corrisponding to a period of 200 nS). Then, find the (approximate) maximum Clock frequency for which the counter

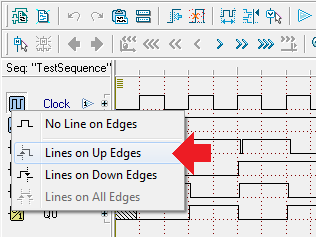

is still working correctly.  (on the left side of the diagram), choosing the command that places the Lines on Up Edges, as you see in the next figure:

(on the left side of the diagram), choosing the command that places the Lines on Up Edges, as you see in the next figure:

, as shown here:

, as shown here: