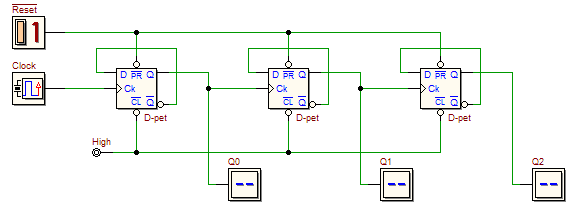

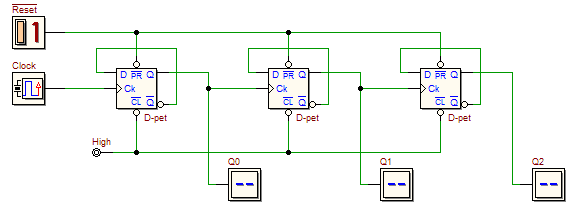

| The sequential network represented in the next figure is a asynchronous counter. Click on the figure to open in the d-DcS a trace of the schematic, and then complete it as shown.

Note that the !Q output of each flip-flop is back-connected

to the D input of the same one, and observe also how

the Ck inputs are connected.

A)

Once completed the schematic, using the timing simulation  ,

verify the network behaviour (a test sequence is available in the Timing Diagram window, containing only the !Reset activation). Observe the direction of the count: is this an "Up-Counter" or a "Down-Counter"? ,

verify the network behaviour (a test sequence is available in the Timing Diagram window, containing only the !Reset activation). Observe the direction of the count: is this an "Up-Counter" or a "Down-Counter"?

Compile a table, as

the following one, that will describe the numerical sequence generated

on Q2Q1Q0 (Q2 = MSB, Q0 = LSB). Fill the last two columns with the decimal representation of the number: one as unsigned number, the other as signed number (two-complement coded):

Binary |

Decimal |

Q2 |

Q1 |

Q0 |

Unsigned |

Signed |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B)

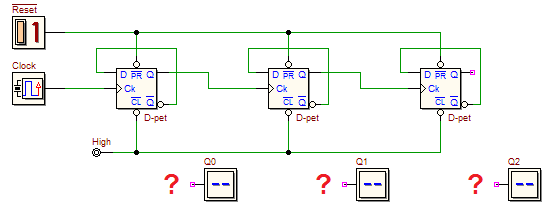

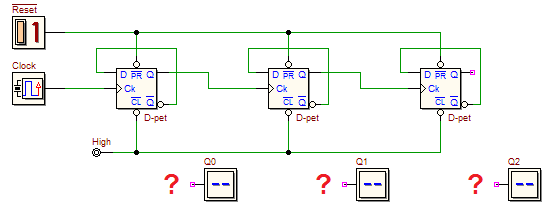

Observe, in the next figure, a network identical to the one before examinated, but with the outputs Q2, Q1 and Q0 unconnected. Open in the d-DcS, with a click on the figure, the schematic to be completed:

Now, complete the new schematic assigning as outputs the !Q of the flip-flops. Using the timing simulation  ,

verify the network behaviour. ,

verify the network behaviour.

How does the counting sequence change?

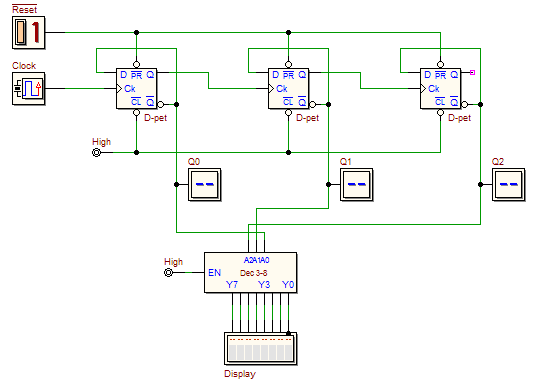

C)

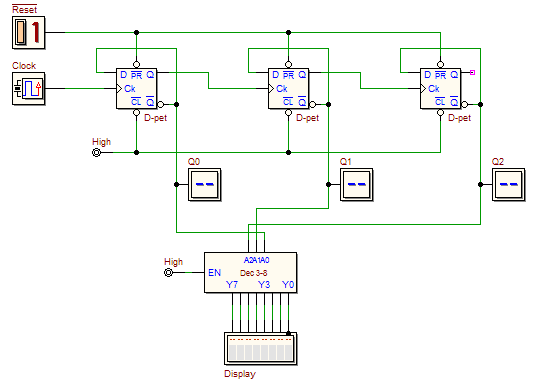

In the following figure, the counter drives a decoder 3-8. The decoder outputs are visualized by a 8-LED binary display (open the schematic in the d-DcS, with a click on the figure):

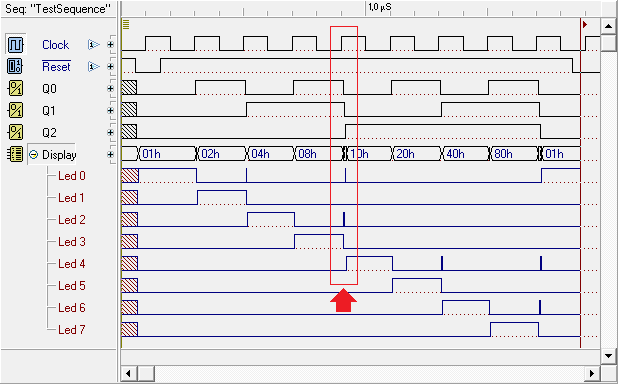

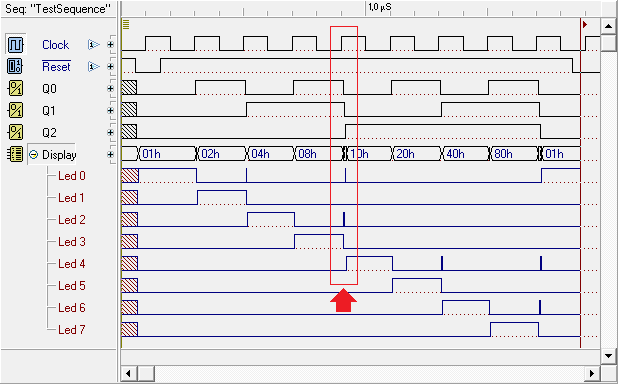

Simulate the circuit by animation  : this could be useful to understand the behavior of the network. In this mode of simulation, it seems to be perfectly operating: but a timing simulation : this could be useful to understand the behavior of the network. In this mode of simulation, it seems to be perfectly operating: but a timing simulation  will proof the limits of the asynchronous implementation of counters (observe the "spurious" outputs): will proof the limits of the asynchronous implementation of counters (observe the "spurious" outputs):

Use the Home cursor  to position the diagram view on the point of interest. Enlarge the timing scale to point out the behavior of the outputs in the critical transitions. In particular, analyse the transition between the activation of LED 3 and LED 4. Try to explain what happens around this transition. to position the diagram view on the point of interest. Enlarge the timing scale to point out the behavior of the outputs in the critical transitions. In particular, analyse the transition between the activation of LED 3 and LED 4. Try to explain what happens around this transition.

|

,

verify the network behaviour (a test sequence is available in the Timing Diagram window, containing only the !Reset activation). Observe the direction of the count: is this an "Up-Counter" or a "Down-Counter"?

,

verify the network behaviour (a test sequence is available in the Timing Diagram window, containing only the !Reset activation). Observe the direction of the count: is this an "Up-Counter" or a "Down-Counter"?

: this could be useful to understand the behavior of the network. In this mode of simulation, it seems to be perfectly operating: but a timing simulation

: this could be useful to understand the behavior of the network. In this mode of simulation, it seems to be perfectly operating: but a timing simulation

to position the diagram view on the point of interest. Enlarge the timing scale to point out the behavior of the outputs in the critical transitions. In particular, analyse the transition between the activation of LED 3 and LED 4. Try to explain what happens around this transition.

to position the diagram view on the point of interest. Enlarge the timing scale to point out the behavior of the outputs in the critical transitions. In particular, analyse the transition between the activation of LED 3 and LED 4. Try to explain what happens around this transition.