| ||

| Trasmettitore e ricevitore seriale su FPGA |

|

|

| v1.92 |

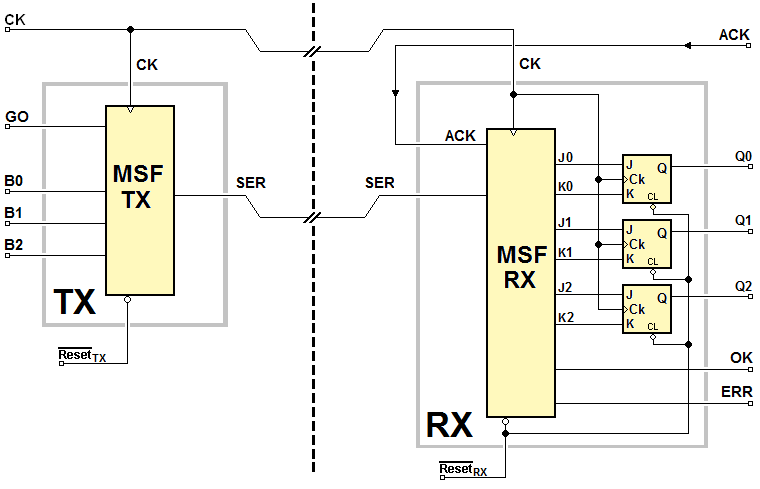

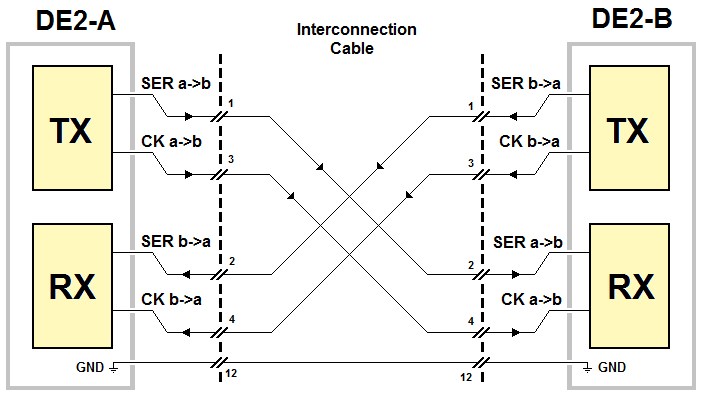

Questa esercitazione propone il progetto di un semplice sistema di comunicazione seriale, basato su due macchine a stati finiti e alcuni flip-flop. Dopo la verifica del progetto mediante simulazione, l'esercitazione conduce alla realizzazione fisica del prototipo su FPGA e alla verifica del suo funzionamento. L'architettura del sistema è rappresentata in figura:

Il sistema è composto da due parti fisicamente separate, un trasmettitore (TX) che pilota la linea seriale SER e un ricevitore (RX) che la riceve. Le due porzioni del sistema sono collegate dalla linea SER e condividono il clock CK.

Specifiche del trasmettitore TX

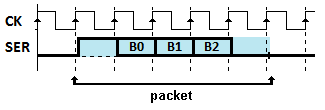

TX riceve dall’esterno tre bit da trasmettere (B0, B1 e B2). Ad ogni fronte di discesa del segnale GO, la cui durata non è precisata, il TX genera sulla linea SER un pacchetto seriale, formato da un bit di START ad “1”, seguito in sequenza dai bit B0, B1 e B2 e terminato da un bit di STOP a “0” (vedi figura seguente). Ciascun bit ha la duratadi un ciclo del clock di sistema.

Specifiche del ricevitore RX

Il ricevitore RX è formato dalla MSF RX e tre flip-flop di tipo logico JK PET. RX attende che gli giunga un pacchetto sulla linea SER, e quindi ne estrae i bit di informazione rendendoli disponibili in parallelo sulle tre uscite Q0, Q1 e Q2 dei flip-flop.

Se il bit di STOP è ricevuto correttamente a “0”, il ricevitore attiva l’uscita OK e la mantiene attiva fino all'attivazione dell'ingresso ACK (attivo basso) oppure fino all'arrivo di un nuovo pacchetto sulla linea SER.

Se il bit di STOP è ricevuto a “1”, il ricevitore attiva ERR e la mantiene attiva fino al ritorno a “0” della linea SER.

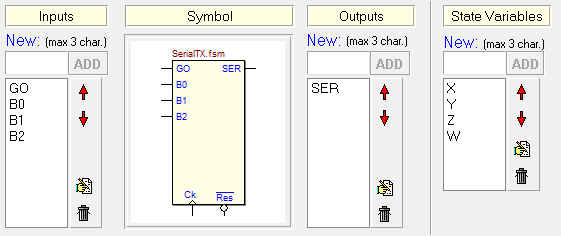

E' disponibile una traccia del diagramma ASM del trasmettitore (un click sulla figura seguente la aprirà nel Deeds-FsM). Le variabili di stato X,Y, Z e W, l'uscita SER, e gli ingressi GO, B0, B1 e B2 sono già stati definiti (il comando  consente di verificare le impostazioni):

consente di verificare le impostazioni):

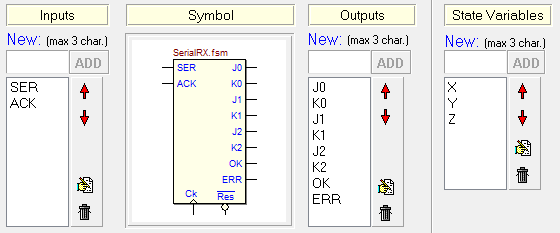

E' disponibile una traccia del diagramma ASM del ricevitore (un click sulla figura seguente la aprirà nel Deeds-FsM). Nella traccia, le variabili di stato X,Y e Z, le uscite J0, K0, J1, K1, J2, K2, OK, ERR, e gli ingressi SER, B0, e ACK sono già stati definiti (il comando  consente di verificare le impostazioni):

consente di verificare le impostazioni):

Verificate, utilizzando la simulazione temporale del d-FsM, che le funzionalità delle due MSF progettate corrispondano alle specifiche.

Terminato il progetto, potete importare i componenti ottenuti nel d-DcS. A questo proposito sono disponibili alcune tracce di schema. Le prime due riportano lo schema del solo trasmettitore e del solo ricevitore: sono utili per verificarne singolarmente il funzionamento mediante simulazione temporale. La terza traccia rappresenta il sistema completo, composto di trasmettitore e di ricevitore, che sono connessi attraverso la linea seriale e condividono il clock. Per ognuna delle tracce, è disponibile, nel diagramma temporale, una appropriata sequenza di test.

A questo punto inizia la procedura per realizzare fisicamente il progetto sulla scheda FPGA. La procedura generale è descritta passo passo nei tutorial introduttivi:

Realizzazione di un prototipo di circuito su scheda Altera DE2

Realizzazione di un prototipo di circuito su scheda Altera DE2

Test di una rete sequenziale su scheda Altera DE2

Test di una rete sequenziale su scheda Altera DE2

Per rendere il progetto più interessante, realizziamo un sistema di comunicazione tra due schede FPGA separate, che permetta di scambiare dati in entrambe le direzioni: il trasmettitore della prima scheda sarà collegato al ricevitore della seconda, e viceversa, mediante un cavo multifilare:

Realizzeremo il collegamento tramite uno dei due connettori da 40 piedini disponibili su ciascuna scheda. Come si vede nella figura qui sopra, abbiamo un collegamento incrociato trasmettitore - ricevitore, in entrambe le direzioni, per un totale di 5 fili (compreso il riferimento di massa GND). Il clock di ciascun trasmettitore è collegato al corrispondente ricevitore, per consentire a quest'ultimo di campionare i dati seriali con lo stesso clock con cui sono trasmessi. Qui lo schema della connessione.

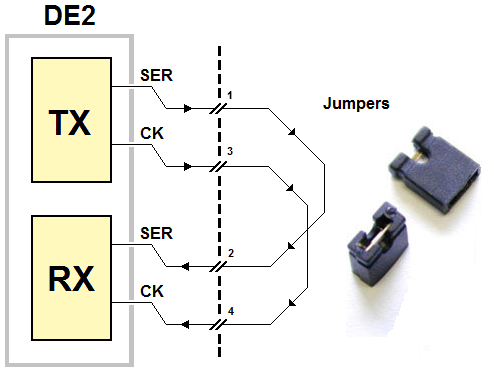

Possiamo effettuare test preliminari con una sola scheda, utilizzando dei semplici ponticelli ("jumpers") inseriti sul connettore, come si vede nella figura seguente, in modo da collegare insieme trasmettitore e ricevitore:

Per rendere possibile la sperimentazione, sia con due schede, sia con una sola, vi proponiamo uno schema modificato, da completare con i vostri componenti TX e RX. Rispetto allo schema che avete utilizzato per la simulazione, sono state modificate le connessioni, ed aggiunte alcune terminazioni: gli ingressi e le uscite del collegamento seriale, più alcune uscite (da collegare a dei LED). Si raccomanda di usare lo schema fornito senza modificare le terminazioni di ingresso e di uscita, perchè sono state predisposte per la esportazione del progetto sulla scheda FPGA.

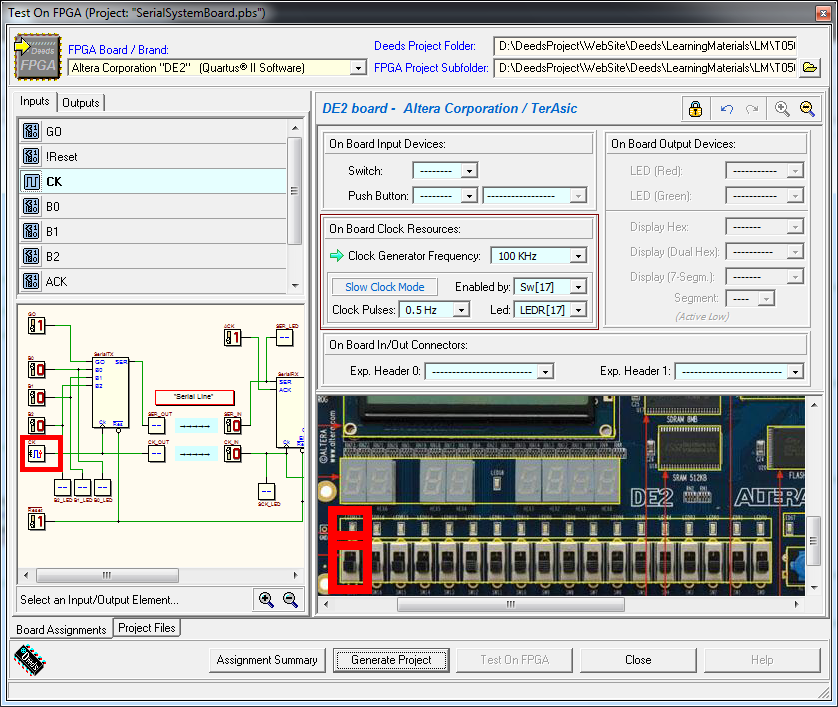

Non appena completato il nuovo schema nel d-DcS, si prosegue con il comando "Test on FPGA" del d-DcS , che apre la finestra di dialogo visibile qui sotto:

Le associazioni tra schema d-DcS e scheda FPGA, per quanto riguarda gli ingressi e le uscite, sono state già definite nella traccia d-DcS fornita, per cui non è necessario modificarle.

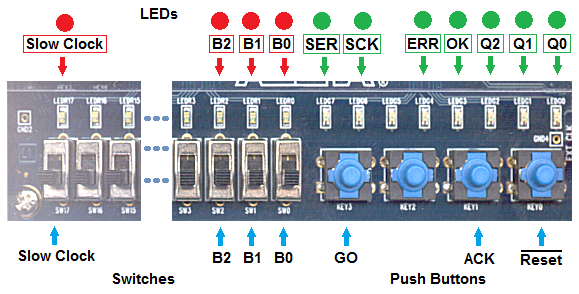

Il clock CK è impostato a 100 KHz (che corrisponde ad un tempo di bit di 10 microsecondi). E' stata anche scelta la modalità "Slow Clock Mode": come risulta dai parametri impostati, visibili nella figura, tale modalità è attivabile tramite l'interruttore SW[17]. Lo "Slow Clock" è impostato alla frequenza di 0,5 Hz, ed è visualizzato dal led rosso LEDR[17]. In base a questa impostazione, se l'interruttore è a zero, il clock CK lavorerà normalmente a 100 Hz; se l'interruttore è a uno, la frequenza del clock sarà ridotta a 0,5 Hz, permettendo di esaminare il funzionamento del nostro circuito con la semplice osservazione visiva.

Si suggerisce di provare ad impostare diversamente la modalità Slow Clock, per esempio assegnando a tale clock, invece che la frequenza di 0,5 Hz, un pulsante (sulla nostra scheda rimane disponibile ancora il pulsante Key[2]). In questo modo, una semplice pressione del pulsante produce un impulso di clock, mentre mantenendo premuto il pulsante si genera una successione di impulsi (questa modifica implica la necessità di ripetere la procedura di generazione del progetto).

Si noti che la programmabilità della frequenza del clock non è una particolarità della scheda FPGA in uso, ma che è realizzata dal processo di esportazione del progetto, che aggiunge al nostro circuito una rete, basata su contatori, che consente di "scalare" a frequenza bassa il clock a 50 MHz di cui è dotata la scheda.

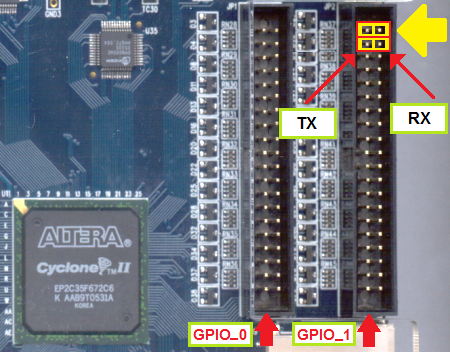

Come descritto in precedenza, il progetto è stato impostato in modo da utilizzare alcuni piedini di uno dei due connettori ("GPIO_1") di espansione presenti sulla scheda, per le uscite del trasmettitore TX e per gli ingressi del ricevitore RX. Nel caso in cui si voglia provare il sistema su di una sola scheda DE2, dobbiamo inserire due ponticelli (jumpers) per unire le linee del trasmettitore con quelle del ricevitore, come evidenziato nella figura seguente, dalla freccia gialla. Altrimenti si tratta di utilizzare il cavo multifilare (descritto in precedenza) e collegare insieme due schede.

Si faccia molta attenzione nel piazzare e rimuovere i ponticelli, per evitare di danneggiare meccanicamente i piedini del connettore. Per evitare possibili danni al chip FPGA, i cui piedini sono direttamente collegati al connettore, è necessario eseguire tale operazione a scheda spenta (non alimentata). Per la comodità dello sperimentatore, le associazioni ai dispositivi di ingresso/uscita sono visualizzate anche nella figura seguente, che può essere considerata come il "pannello di controllo" del sistema realizzato, utile per eseguirne il test:

Usando gli interruttori e i pulsanti qui sopra indicati, ed osservando l'accensione dei LED, è possibile verificare il funzionamento del sistema.