|

|

||||||||||

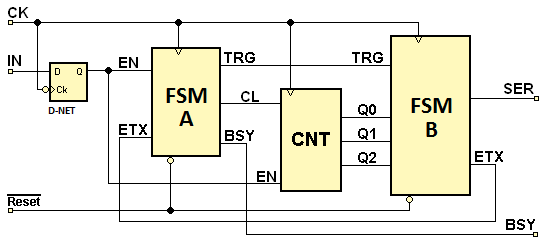

| Progettare il sistema digitale la cui architettura è rappresentata in figura. Il sistema riceve in ingresso un segnale IN, normalmente a zero, sul quale si presentano impulsi a livello uno di durata variabile da uno a sette periodi del segnale di clock CK.

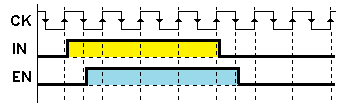

Il flip-flop D-net, visibile in alto a sinistra, re-sincronizza sul fronte di discesa del clock le sequenze di bit ricevute. Il diagramma temporale qui sotto mostra un impulso sull'ingresso IN della durata di quattro periodi, e la corrispondente uscita EN del flip-flop.

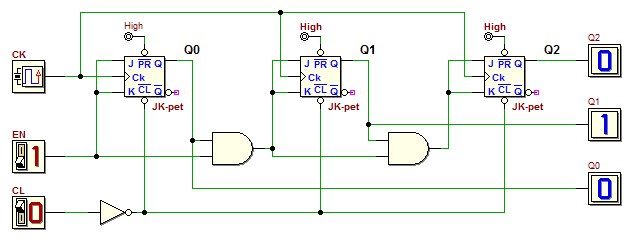

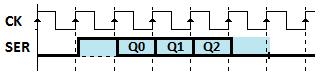

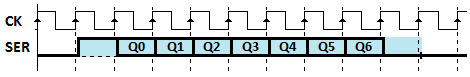

Il sistema misura la durata degli impulsi, in termini di periodi di clock, e trasmette il valore della misura sulla linea seriale SER. Per la misura della durata degli impulsi il sistema utilizza il contatore CNT, il cui schema è riportato nella figura seguente (con un click sulla figura potete caricare lo schema del contatore nel d-DcS per analizzarne il funzionamento). Nel sistema, il contatore CNT è sincronizzato dallo stesso clock CK della macchina a stati finiti FSM-A e da questa riceve il clear asincrono CL. La FSM-A segnala alla FSM-B, attivando per un periodo di CK il segnale TRG, che la misura della durata dell'impulso è terminata e il valore del conteggio è disponibile sulle uscite Q2, Q1 e Q0 del contatore stesso. Quando necessario, la FSM-A azzera il contatore CNT tramite il segnale CL; inoltre, per tutto il tempo in cui il sistema è impegnato nella ricezione dell’impulso e nella trasmissione su SER, la FSM-A attiva BSY. La FSM-B inizia a generare l’uscita SER quando riceve l’impulso TRG. Il dato seriale in uscita è formato da un bit di start a '1', i tre bit Q0, Q1, Q2 (LSB in testa) con la durata dell'impulso e un bit di stop a '0', come rappresentato nella figura seguente.

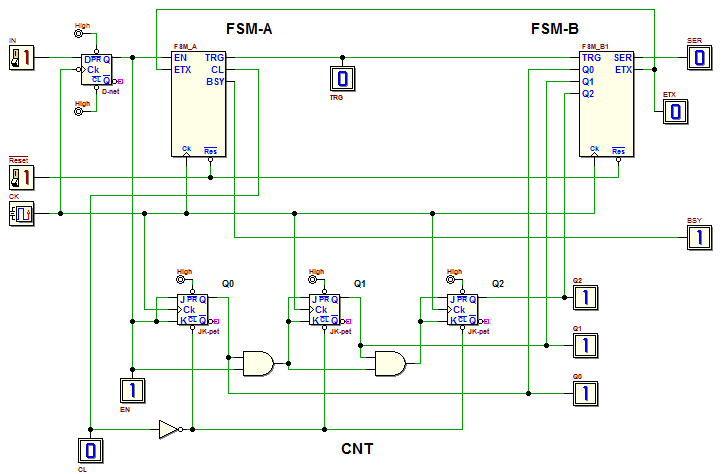

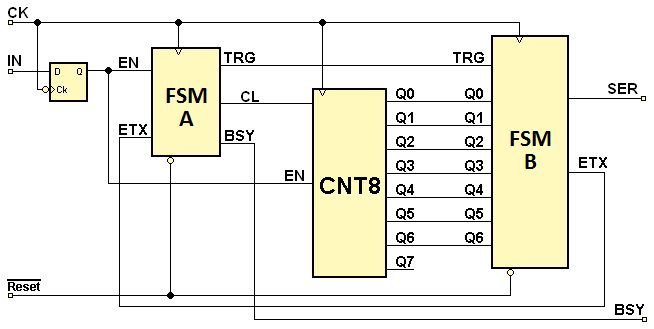

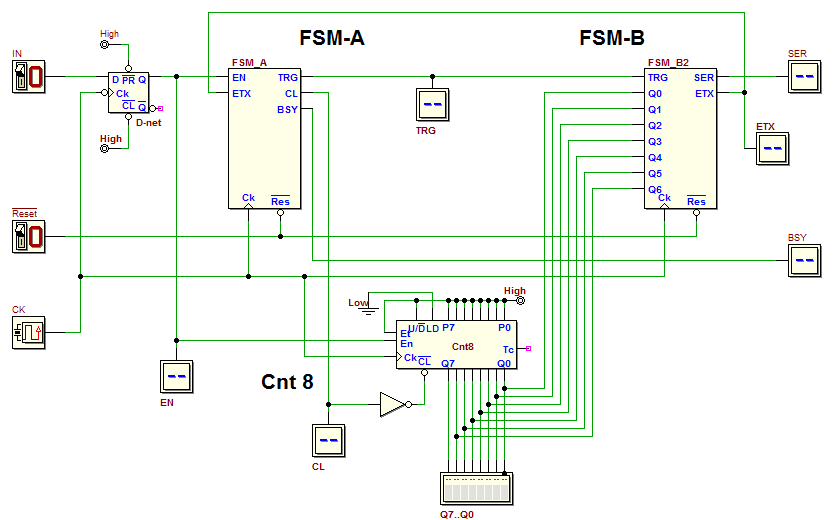

Inoltre, la FSM-B genera l'uscita ETX per informare la FSM-A della fine della trasmissione su SER. Si chiede di progettare e simulare, utilizzando il d-FsM, la FSM-A e la FSM-B. Qui sono disponibili le tracce dei diagrammi ASM della FSM-A e della FSM-B. Infine, si disegni lo schema d-DcS dell'intero sistema, utilizzando i componenti generati dal d-FsM. Un click sulla figura seguente aprirà nel d-DcS lo schema da completare (nella finestra del diagramma temporale è disponibile una sequenza di test per effettuare la simulazione del sistema): Nota: gli impulsi su IN sono separati tra loro da un numero di periodi di clock sufficienti a permettere al sistema di completare la trasmissione del dato, prima che un altro impulso si presenti all’ingresso; la durata di un impulso non è mai superiore a sette periodi del clock CK. Seconda versione (misurazione estesa) In figura è rappresentata una versione modificata del misuratore della durata dell'impulso. Con questo dispositivo possiamo misurare impulsi di durata variabile da 1 a 127 periodi del segnale di clock CK.

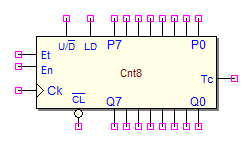

Questo sistema utilizza un contatore più grande del precedente, presente nella libreria del d-DcS, e denominato "Cnt8". Nella figura seguente è visibile il simbolo di tale componente (qui una descrizione del suo funzionamento).

Nel sistema, il contatore Cnt8 è utilizzato con lo stesso criterio del contatore Cnt del precedente circuito, e il valore del conteggio è disponibile sulle uscite Q6, Q5, Q4, Q3, Q2, Q1 e Q0 del contatore stesso (Q7 non è utilizzato). Il resto delle specifiche è identico. La FSM-A è identica a quella della precedente realizzazione, mentre la FSM-B si differenzia solo nel numero di bit contenuti nel pacchetto generato sull’uscita SER: un bit di start a '1', sette bit Q0, Q1, Q2, Q3, Q4, Q5, Q6 e un bit di stop a '0', come visibile nella figura seguente:

Si chiede di progettare e simulare, utilizzando il d-FsM, la nuova FSM-B (qui il diagramma ASM, da completare, della FSM-B). Infine, si completi lo schema del sistema modificato, visibile nella figura seguente. Un click sulla figura aprirà nel d-DcS lo schema da completare (nella finestra del diagramma temporale è disponibile una sequenza di test per effettuare la simulazione del sistema): | |||||||||||