|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

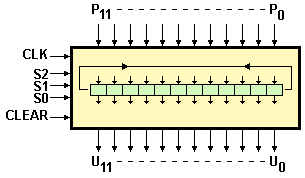

| In questo laboratorio scriveremo un programma in assembly DMC8 che emula un Registro/Contatore a 12 bit (vedi la figura qui sotto). Eseguiremo le opportune verifiche di funzionalità, non solo in simulazione, ma anche realizzandone un prototipo su scheda FPGA.

Il nostro Registro/Contatore ha le seguenti terminazioni di ingresso/uscita:

Quando il CLEAR sincrono è attivo, le uscite del componente sono azzerate sul fronte di salita del clock. Quando CLEAR non è attivo, a seconda della funzione impostata su S2,S1,S0, il componente lavora come registro parallelo, oppure come registro a scorrimento a rotazione o, ancora, come contatore ciclico avanti/indietro. Quando la funzione richiesta cambia, il componente non perde lo stato in cui si trova (ricordiamoci che il componente reale è basato su flip-flop). La tabella seguente descrive nel dettaglio le funzioni svolte dal componente:

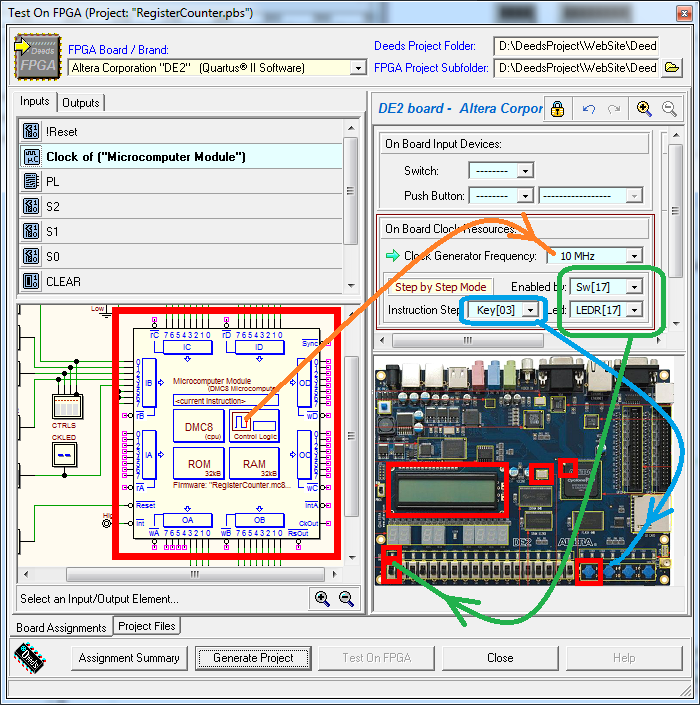

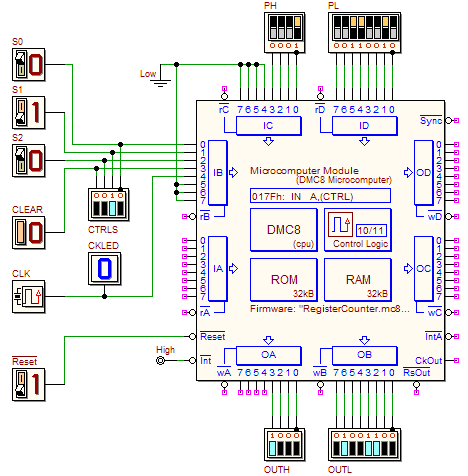

Per emulare il dispositivo, configuriamo un microcomputer come visibile nello schema seguente (un click sulla figura lo aprirà nel d-DcS): Utilizziamo tre porti paralleli di ingresso (IB, IC e ID) e due porti paralleli di uscita (OA e OB). Le linee CLK, CLEAR, S2, S1 e S0 sono connesse rispettivamente ai bit 4, 3, 2, 1 e 0 del porto di ingresso IB, le linee P11..P0 ai porti di ingresso IC e ID, e le linee U11..U0 ai porti di uscita OA e OB. Il programma è lanciato alla attivazione del Reset hardware. Due differenti tracce del codice, da completare nel d-McE, sono disponibili qui: la prima è più impegnativa; la seconda contiene più suggerimenti. Completata la scrittura del programma, ne potremo testare la funzionalità nel debugger del d-McE. A questo punto, caricheremo il programma nella ROM del microcomputer, per simulare il sistema nel d-DcS in modalità temporale A questo punto inizia la procedura per realizzare fisicamente il progetto sulla scheda FPGA. La procedura generale è descritta passo passo nei tutorial introduttivi: Il comando "Test on FPGA" (del d-DcS) apre la finestra di dialogo visibile qui sotto:

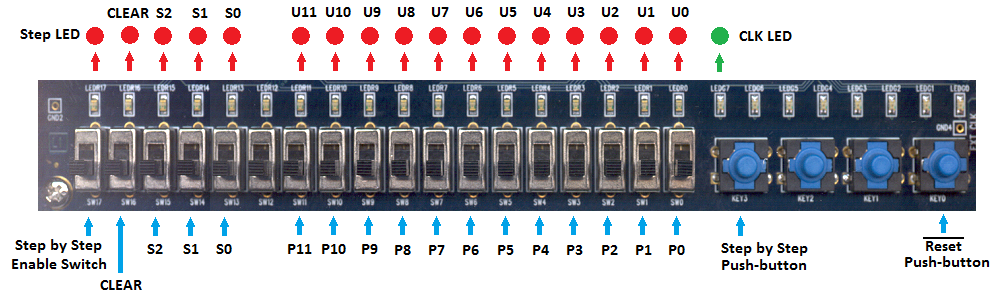

Si noti che tutte le associazioni degli ingressi e uscite con i corrispondenti dispositivi della scheda FPGA sono state già predefinite, e non è necessario modificarle. La frequenza di clock è stata definita pari a 10 MHz. E' stata predisposta la modalità di esecuzione passo-passo ("Step by Step Mode"), assegnando l'interruttore Sw[17] al compito di abilitare (al "run time") tale funzione. E' stato predisposto un LED, il LEDR[17], come visualizzatore degli impulsi di clock che saranno inviati al microcomputer. Infine, è stato scelto il pulsante Key[03] come comando manuale dell'avanzamento delle istruzioni. Se l'interruttore Sw[17] è posto a '0', la funzione di debug non è attiva e il microcomputer funziona con il clock "normale" (10 MHz). Se l'interruttore Sw[17] è a '1', il clock del processore è inibito, e il sistema di debug resta in attesa che l'utente prema il pulsante Key[03] (a ogni pressione del pulsante, il microcomputer esegue una istruzione). Per ottimizzare la sperimentazione di quanto descritto sulla scheda FPGA, le associazioni sono evidenziate in modo riassuntivo nella figura seguente (il "pannello di controllo" del nostro sistema):

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

(una adeguata sequenza di test è disponibile nella finestra del diagramma temporale). Si raccomanda di non apportare modifiche alle terminazioni di ingresso e uscita, che sono state preimpostate per il prossimo passo: l'esportazione del progetto su di una scheda FPGA.

(una adeguata sequenza di test è disponibile nella finestra del diagramma temporale). Si raccomanda di non apportare modifiche alle terminazioni di ingresso e uscita, che sono state preimpostate per il prossimo passo: l'esportazione del progetto su di una scheda FPGA.