|

|

||||||||||

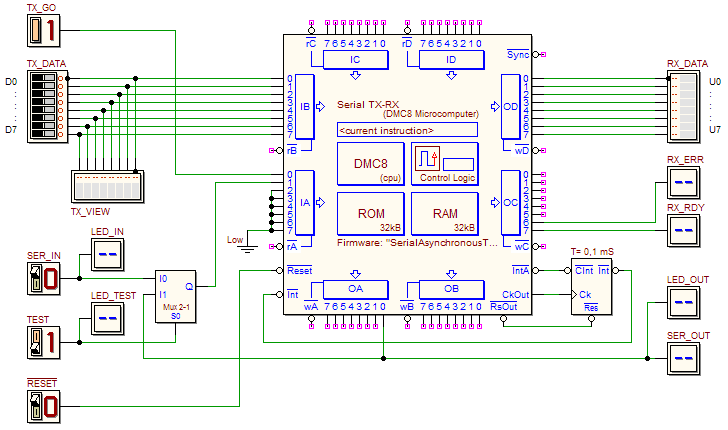

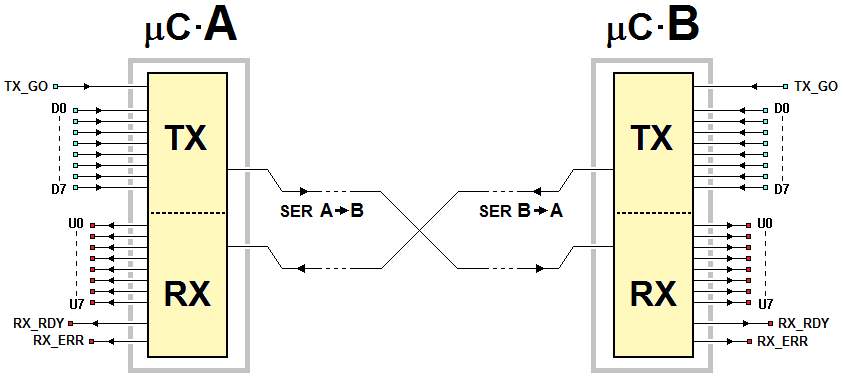

| In questo laboratorio si chiede di completare il progetto di un sistema di comunicazione seriale asincrona basato su microcomputer. Dopo la verifica del progetto mediante simulazione, ne realizzeremo un prototipo su FPGA per verificarne il reale funzionamento. L'architettura del sistema è riportata in figura:

Il sistema è composto da due microcomputer Nella figura seguente è visibile lo schema di ogniuno dei due microcomputer:

In figura sono visibili, dall'alto e da sinistra:

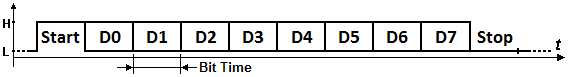

Nella figura è visibile inoltre, sulla destra in basso, la presenza di un componente Interrupt Timer, predisposto per interrompere ciclicamente il microprocessore ogni 0,1 mS. Specifiche del modulo trasmettitore TX TX legge i bit di dato da trasmettere (D0 ... D7) tramite il porto IB. Al fronte di salita del segnale TX_GO, letto sul bit 0 del porto IA, il modulo TX genera sulla linea SER_OUT una sequenza seriale, il cui pacchetto è formato da un bit di START a '1', seguito, nell'ordine, dai bit D0, D1, D2, D3, D4, D5, D6 e D7 e, infine, terminato con un bit di STOP a “0”, come visibile nella figura seguente:

Il tempo di bit ("Bit Time") è pari a 1,6 mS, pari a 16 volte l'intervallo di tempo scandito dal componente Interrupt Timer. Il segnale di comando TX_GO ha una durata minima pari a 2 mS (la durata massima non è precisata). Specifiche del modulo ricevitore RX Il ricevitore RX attende l'arrivo di pacchetti seriali sulla linea SER_IN (si suppone che l'ingresso TEST sia impostato a '0'). Non appena individuato l'inizio di un pacchetto (bit di Start a '1'), il ricevitore sincronizza l'acquisizione dei dati e, nell'ordine, estrae dal pacchetto gli otto bit di informazione, rendendoli infine disponibili in parallelo sulle uscite U0..U7 (tramite il porto OD). Infine, se il bit di STOP è ricevuto correttamente a '0', il ricevitore attiva l’uscita RX_RDY per un tempo pari a 1,6 mS; altrimenti, se il bit di STOP è a '1', il ricevitore attiva RX_ERR e la mantiene attiva fino al ritorno a '0' della linea SER_IN. L'ingresso TEST permette di scegliere la sorgente della sequenza seriale da decodificare. Se l'ingresso di TEST è attivato, la sequenza seriale proviene dalla linea SER_OUT del proprio trasmettitore. In questa modalità possiamo verificare la funzionalità del sistema di trasmissione/ricezione in loco, senza la necessità di collegarci ad un secondo sistema. Sono qui disponibili due tracce di possibili soluzioni, in codice assembly DMC8, in ordine decrescente di difficoltà:

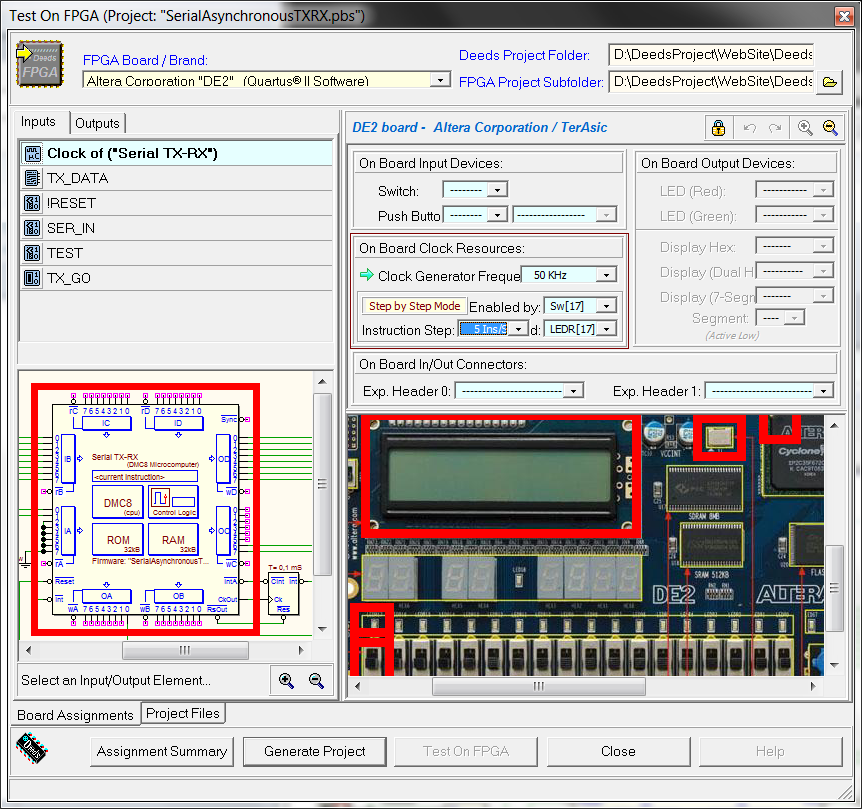

Chi volesse eseguire solo un'analisi di codice già scritto, e simularne il comportamento, trova disponibile qui anche una soluzione completa. Al termine della scrittura e del test funzionale del programma nel d-McE, occorre programmare la ROM del microcomputer (potete aprirne lo schema nel d-DcS con un click qui). Nella finestra del diagramma temporale del d-DcS è disponibile una appropriata sequenza di test. Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perché sono state predisposte per la esportazione del progetto sulla scheda FPGA. A questo punto inizia la procedura per realizzare fisicamente il progetto sulla scheda FPGA. La procedura generale è descritta passo passo nei tutorial introduttivi: Il comando "Test on FPGA" (del d-DcS) apre la finestra di dialogo visibile qui sotto:

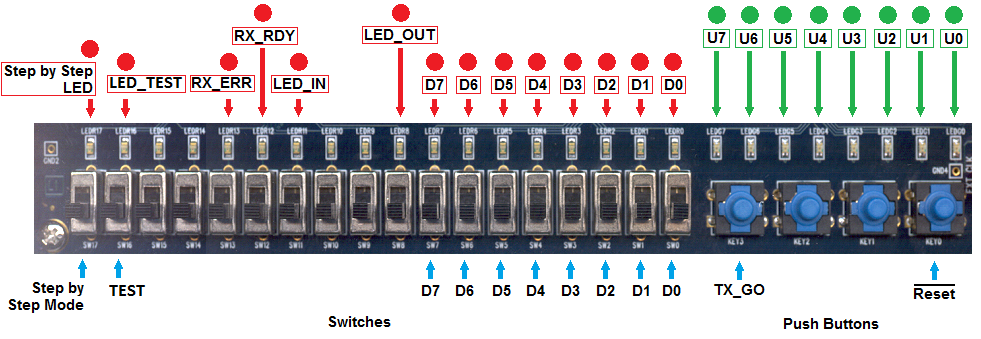

Si noti che tutte le associazioni degli ingressi e uscite con i corrispondenti dispositivi della scheda FPGA sono state già predefinite, e non è necessario modificarle. Per quanto riguarda il clock del microcomputer, come potrete verificare, è pre-impostato a 50 KHz (si tratta di una frequenza sufficientemente bassa per consentire di osservare a occhio nudo la serializzazione e de-serializzazione dei bit). Nulla vieta di reimpostare, in un secondo momento, la frequenza del clock a quella nominale (10 MHz). E' stata anche impostata la modalità "Step by Step Mode", prevista per il microcomputer: come risulta dai parametri impostati, sono stati selezionati un interruttore e un LED rosso (SW[17]e LEDR[17], rispettivamente, cioè i primi in basso a sinistra nella scheda), e una frequenza di esecuzione delle istruzioni pari a 5 al secondo. Questo significa che se l'interruttore prescelto è a zero (SW[17], levetta verso di noi), il clock CK lavora normalmente a 50 KHz, ma se l'interruttore è a uno (levetta nell'altro senso), viene attivato un apposito circuito ausiliario (un debugger) che consente di eseguire un'esecuzione rallentata delle istruzioni, a scopo diagnostico. L'esecuzione delle istruzioni, nel tempo, è segnalata dal LED prescelto (LEDR[17]). Per ottimizzare la sperimentazione di quanto descritto sulla scheda FPGA, le associazioni sono evidenziate in modo riassuntivo nella figura seguente (il "pannello di controllo" del nostro sistema):

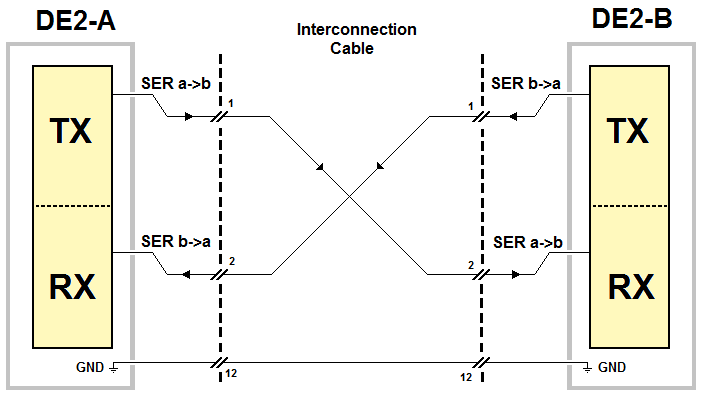

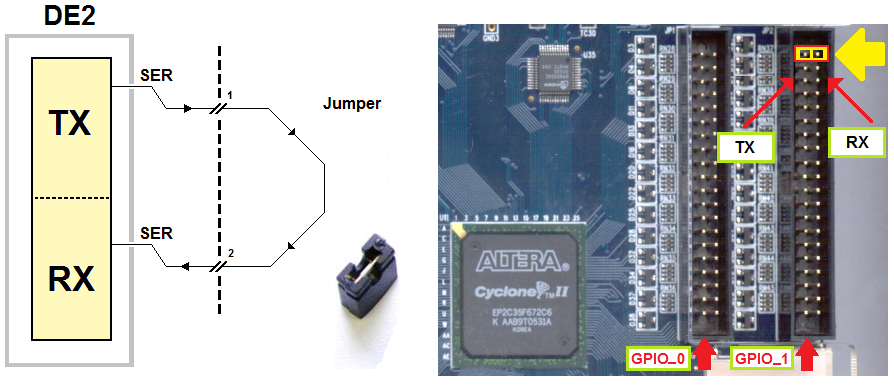

Possiamo verificare il funzionamento del sistema da solo, attivando la modalità di test (interruttore di TEST verso l'alto), oppure utilizzando due schede separate, interconnesse mediante un cavo adeguato, tale da scambiare dati in entrambe le direzioni: Realizziamo il collegamento tramite uno dei due connettori da 40 piedini disponibili su ciascuna scheda FPGA. Come si vede nella figura qui sopra, utilizziamo un collegamento incrociato tra il trasmettitore e il ricevitore, in entrambe le direzioni, per un totale di 3 fili (compreso il riferimento di massa GND). Qui lo schema della connessione, che fa riferimento al connettore di espansione "GPIO_1" presente sulla scheda. Anche senza utilizzare l'interruttore TEST, possiamo eseguire test preliminari con una sola scheda, utilizzando un semplice ponticello ("Jumper") inserito sul connettore, come si vede nella figura seguente (freccia gialla), in modo da collegare insieme trasmettitore e ricevitore: Si faccia molta attenzione nel piazzare e rimuovere il ponticello, per evitare di danneggiare meccanicamente i piedini del connettore. Per evitare possibili danni al chip FPGA, i cui piedini sono direttamente collegati al connettore, è necessario eseguire tale operazione a scheda non alimentata (spenta). | |||||||||||

e

e  identici, interconnessi tra di loro attraverso due linee. Ogni microcomputer comprende moduli software che realizzano, con tecniche di interrupt, un trasmettitore (TX) e un ricevitore (RX) di linea seriale. I microcomputer lavorano con clock alla stessa frequenza (10 MHz), ma indipendenti tra di loro. Esaminiamo ora le specifiche di progetto dei moduli TX e RX.

identici, interconnessi tra di loro attraverso due linee. Ogni microcomputer comprende moduli software che realizzano, con tecniche di interrupt, un trasmettitore (TX) e un ricevitore (RX) di linea seriale. I microcomputer lavorano con clock alla stessa frequenza (10 MHz), ma indipendenti tra di loro. Esaminiamo ora le specifiche di progetto dei moduli TX e RX.