|

|

||||||||||

|

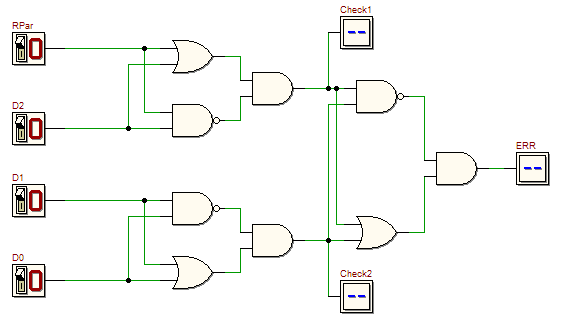

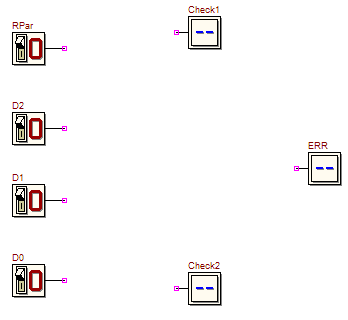

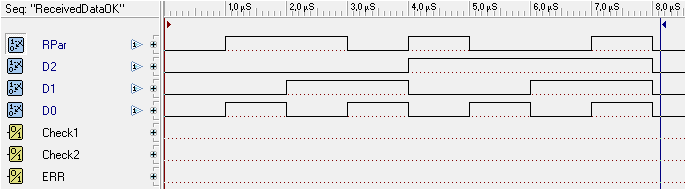

Un click sulla figura aprirà lo schema nel Deeds-DcS: Usando la simulazione per animazione, si ricavi una tavola di verità che descriva il funzionamento della rete. Si scriva l'espressione booleana delle uscite ERR, Check1 e Check2, ricavandola dallo schema (non dalla tavola di verità). ERR può essere espresso in funzione di Check1 e Check2. Un esame della tavola di verità ci consente di semplificare il circuito, che può essere sostituito da una rete impiegante soltanto tre porte EXOR. Si riscriva quindi una nuova espressione per l'uscita ERR in termini di sole porte EXOR (usandola notazione “x EXOR y” oppure “x XOR y”), e si disegni un nuovo schema, completando quello riportato nella figura seguente (un click sulla figura lo aprirà nel Deeds-DcS): Si verifichi la correttezza del funzionamento della nuova rete, utilizzando la simulazione per animazione. La rete può essere utilizzata per verificare che la Parità dei dati D2, D1 e D0, rappresentata dal bit RPar (= Parità Ricevuta), abbia lo stesso valore della Parità calcolata dalla nostra rete. L'uscita ERR è attivata quando RPar e la Parità ricalcolata non corrispondono. E' utile simulare la rete utilizzando la simulazione temporale: suggeriamo di utilizzare le due sequenze di test mostrate qui di seguito (e disponibili nella finestra del diagramma temporale). La prima sequenza di test consente di dimostrare la ricezione di una sequenza corretta:

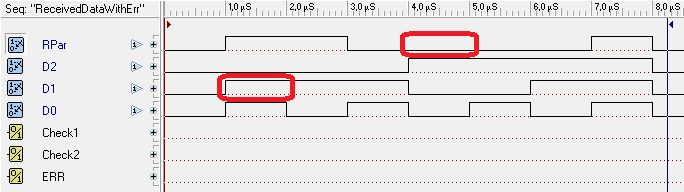

La seconda sequenza di test mostra dei dati ricevuti contenenti degli errori, dovuti alla presenza di disturbi o malfunzionamenti nel sistema che ci trasporta i quattro bit. Dalla simulazione possiamo osservare che, come evidenziato in rosso, due bit sono stati alterati: D1 nel secondo insieme di valori, e RPar nel quinto.

|

|||||||||||