|

|

|||||||||||||||||||||||||||||||||

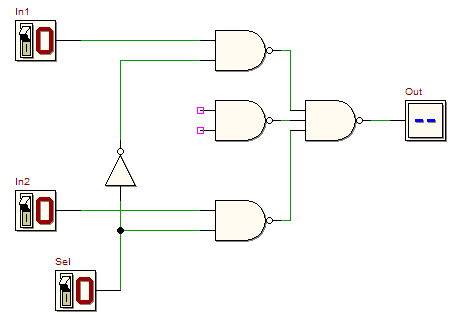

| Si carichi nel d-DcS la rete qui rappresentata, con un click sulla figura: Il circuito è un multiplexer a due ingressi. Si misuri, mediante una simulazione temporale

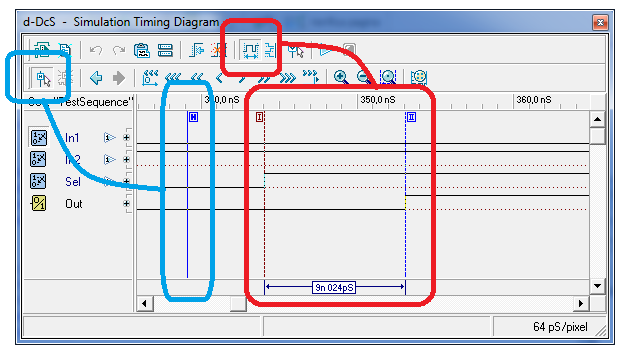

Si suggerisce di utilizzare la sequenza di test disponibile nella finestra del diagramma temporale. Per facilitare la misura del tempo, in questa finestra sono presenti due utili comandi:

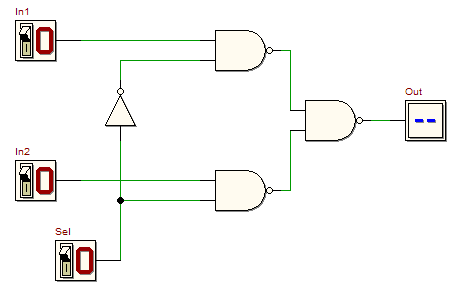

Si noti che, quando In1 e In2 sono a livello alto, una delle transizioni di Sel produce un'alea statica sull'uscita Out. Si misuri la durata dell'alea, analizzando il suo comportamento mediante la simulazione temporale (si utilizzi una adeguata scala di visualizzazione). Usando il metodo della copertura delle transizioni uno-uno, si modifichi il circuito al fine di eliminare l'alea. Si disegni il circuito modificato e si verifichi l'eliminazione dell'alea mediante simulazione (si utilizzi la stessa sequenza e la stessa scala temporale della precedente verifica). E' qui disponibile uno schema da completare (un click sulla figura seguente lo aprirà nel d-DcS): | ||||||||||||||||||||||||||||||||||

, il tempo di propagazione tra il segnale Sel e l'uscita Out, e si compili una tabella come la seguente, dove la prima colonna indica le transizioni dell'ingresso Sel:

, il tempo di propagazione tra il segnale Sel e l'uscita Out, e si compili una tabella come la seguente, dove la prima colonna indica le transizioni dell'ingresso Sel: