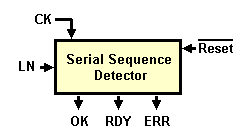

| Il circuito in figura è un riconoscitore di sequenza seriale. Riceve la linea serial LN, e genera tre uscite (OK, RDY e ERR):

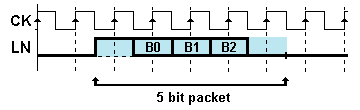

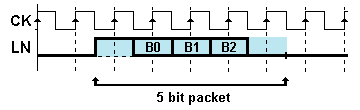

L'ingresso LN riceve dall'esterno una successione di bit, sincroni con il clock, raggruppati in pacchetti di cinque, come rappresentato nella figura seguente:

Ogni pacchetto inizia con il primo bit sempre al valore '1' (start bit), e termina con il quinto bit a '0' (stop bit). Questi due bit non trasportano informazione, ma servono per identificare i 3 bit (B0, B1, B2), che rappresentano i dati contenuti nel pacchetto. Ogni bit ha una durata fissa, chiamata tempo di bit. Nel nostro caso, il tempo di bit è pari al periodo del clock, e i fronti di salita del clock campionano il dato al centro del tempo di bit. L'ingresso LN, a riposo, ha il valore '0'. Inoltre, nel nostro esempio, tra un pacchetto e il successivo vi è una pausa di almeno tre cicli di clock.

Il dispositivo attende l'arrivo del bit di start, per poi ricevere ed elaborare tutti gli altri bit del pacchetto. Lo scopo del dispositivo è riconoscere la sequenza B0, B1, B2 = '0', '1', '1', rispettando le seguenti specifiche:

- Se, a fine sequenza, il bit di stop non è pari a '0' (cioè il pacchetto non è stato ricevuto correttamente), viene attivata l'uscita ERR per la durata di un ciclo di clock;

- Se il pacchetto è ricevuto correttamente, e B0 = '0', B1 = '1' e B2 = '1', il riconoscitore attiva l'uscita OK per la durata di un ciclo di clock;

- In ogni caso, durante l'attesa di un pacchetto, il dispositivo mantiene attiva l'uscita RDY;

- L'attivazione del !Reset asincrono impone alla rete uno stato iniziale definito: quello in cui è in attesa del bit iniziale di un nuovo pacchetto.

Si chiede di:

- Progettare il riconoscitore, mediante il d-FsM (si può utilizzare questa traccia del diagramma ASM, dove ingressi, uscite e variabili di stato sono già state definite);

- Verificare il comportamento della MSF utilizzando il simulatore interno al d-FsM. Si suggerisce di simulare il circuito impostando più sequenze di ingresso, tra cui, ad esempio, il caso del pacchetto contenente la sequenza da riconoscere ('10110'), di un pacchetto con il bit di stop non corretto ('10111') e di un pacchetto contente una sequenza di bit non riconosciuta (p.es. '10000');

- Importare il riconoscitore, come componente, nel d-DcS, completando lo schema qui fornito;

- Ripetere le verifiche anche con il simulatore temporale del d-DcS.

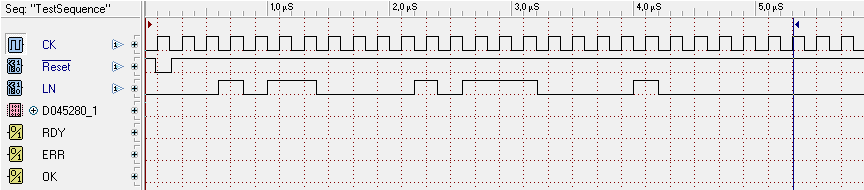

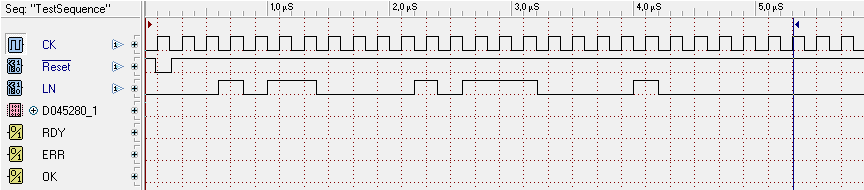

Nota: nel diagramma temporale dello schema d-DcS da completare è stata predisposta la sequenza di test qui rappresentata:

|