| ||

| Progetto di un processore di dati seriali |

|

|

| v1.92 |

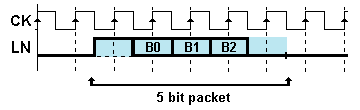

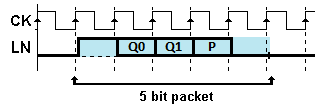

Progettare, mediante il simulatore Deeds-FsM, un sistema digitale sincrono che riceve e ritrasmette dati seriali. L'ingresso LN riceve dall'esterno una successione di bit, sincroni con il clock, raggruppati in pacchetti di cinque, come rappresentato nella figura seguente:

Ogni pacchetto inizia con il primo bit sempre al valore '1' (start bit), e termina con il quinto bit sempre a '0' (stop bit). Questi due bit non trasportano informazione, ma servono per identificare la posizione degli altri 3 bit (B0, B1, B2), che contengono i dati trasportati dalla sequenza. Ogni bit ha una durata fissa, chiamata tempo di bit. Nel nostro caso, il tempo di bit è pari al periodo del clock, e i fronti di salita di questo corrispondono al centro di tale intervallo. L'ingresso LN, a riposo, ha il valore '0'. Il dispositivo attende l'arrivo del bit di start, per poi ricevere ed elaborare tutti gli altri bit del pacchetto.

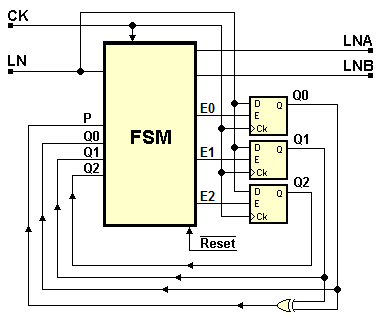

La figura seguente mostra l'architettura del sistema, dove la macchina a stati finiti FSM controlla tre flip-flop di tipo E-PET, che hanno il compito di immagazzinare temporaneamente i bit di informazione ricevuti dalla linea LN (B0 è memorizzato su Q0, B1 su Q1 e B2 su Q2). La macchina a stati pilota le due linee LNA e LNB, su cui saranno generate le sequenze seriali di uscita.

Il sistema controlla che il pacchetto ricevuto sia valido, cioè che termini correttamente con il bit di stop a '0'. Se questa condizione non è verificata, il sistema ignora i dati ricevuti, non attiva le linee di uscita, attende che la linea LN sia tornata a riposo e, infine, si mette in attesa di un nuovo pacchetto.

Se il pacchetto è valido, la macchina a stati utilizza il valore di Q2 per selezionare l'uscita si cui trasmettere (LNA se Q2 = '0', oppure LNB se Q2 = '1'). La sequenza trasmessa, descritta dalla figura seguente, è simile a quella ricevuta, ma il bit B2 è sostituito dal bit P, che rappresenta la parità calcolata su Q0 e Q1 dalla porta EXOR presente nel sistema.

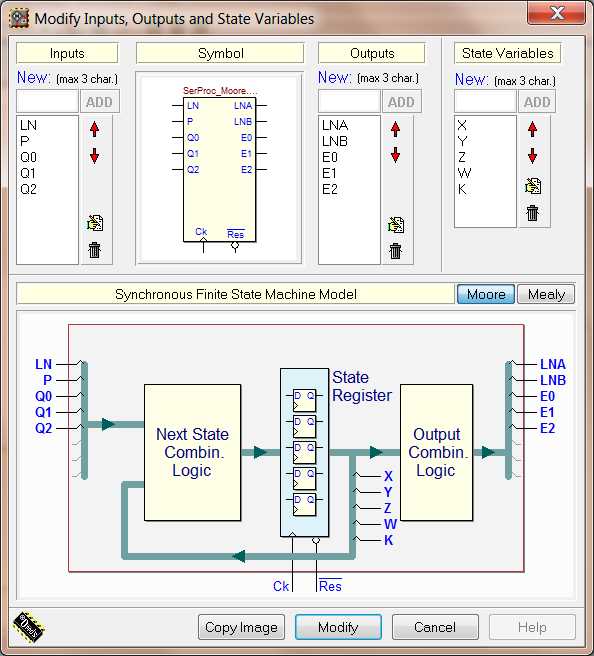

E' disponibile una traccia del diagramma ASM del componente FSM (un click sulla figura seguente la aprirà nel Deeds-FsM). Le variabili di stato X, Y, Z, W e K, le uscite LNA, LNB, E0, E1 e E2, e gli ingressi LN, P, Q0, Q1 e Q2 sono già stati definiti (il comando  consente di verificare le impostazioni e di definire se utilizzare il modello di Mealy o di Moore):

consente di verificare le impostazioni e di definire se utilizzare il modello di Mealy o di Moore):

Dopo aver definito il comportamento del componente mediante il diagramma ASM, lo si testi preliminarmente nel Deeds-FsM stesso, mediante il simulatore temporale incluso. Si completi nel Deeds-DcS, poi, lo schema Deeds-DcS qui fornito, inserendo nella rete il componente FSM progettato.

Infine, si verifichi nel Deeds-DcS il funzionamento dell'intero sistema, utilizzando la simulazione temporale. Si suggerisce di utilizzare, per la verifica, almeno tre sequenze di ingresso: 1) una che dia luogo alla trasmissione sull'uscita LNA, 2) un'altra che coinvolga l'uscita LNB, e 3) una sequenza che non produca trasmissione (queste sequenze di test sono già impostate nello schema Deeds-DcS fornito).

Note: 1) si ipotizzi che, tra due successive sequenze ricevute su LN, trascorra un tempo sufficiente affinchè il sistema sia in grado di completare la trasmissione sulle uscite prima di ricevere un altro pacchetto in ingresso; 2) l'attivazione del !Reset asincrono deve portare la rete nello stato in cui è in attesa di una nuova sequenza.

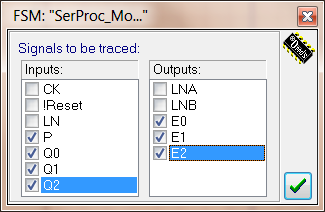

Suggerimento: per facilitare l'analisi della rete, è possibile visualizzare, nel diagramma temporale del Deeds-DcS, gli ingressi e uscite del componente FSM, scegliendoli prima di iniziare la simulazione. E' sufficiente fare click sul nome della traccia, nel diagramma temporale e, tramite l'opportuna voce di menù (Select Signals to Trace), aprire l'apposita finestra di dialogo:

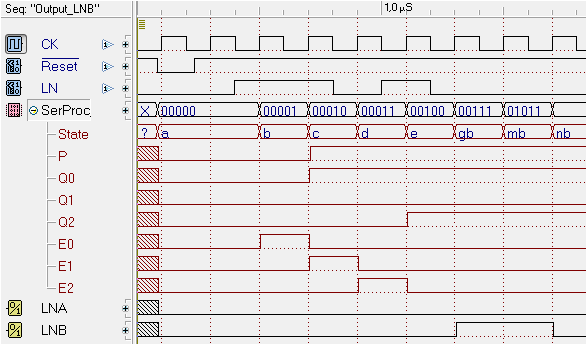

Si ottiene la possibilità di "espandere" la traccia del componente, come rappresentato nella figura sequente: